Jawad Faiz Behzad Siahkolah

# Electronic Tap-changer for Distribution Transformers

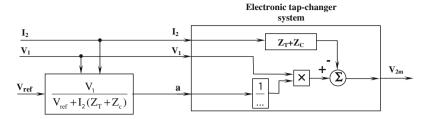

# Power Systems

For further volumes: http://www.springer.com/series/4622

# Electronic Tap-changer for Distribution Transformers

Professor Jawad Faiz School of Electrical and Computer Engineering University College of Engineering. University of Tehran Tehran Iran e-mail: jfaiz@ut.ac.ir

Dr. Behzad Siahkolah Kavandish Company Tehran Iran

e-mail: behzad@kayandish.com

ISSN 1612-1287

ISBN 978-3-642-19910-3

e-ISSN 1860-4676

e-ISBN 978-3-642-19911-0

DOI 10.1007/978-3-642-19911-0

Springer Heidelberg Dordrecht London New York

© Springer-Verlag Berlin Heidelberg 2011

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilm or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

The use of general descriptive names, registered names, trademarks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

Cover design: eStudio Calamar, Berlin/Figueres

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

### **Preface**

Although many papers dealing with electronic tap-changer has been published during the last decades, there is not any comprehensive reference book, dealing with electronic tap-changer in its all aspects in bookshelves. This book is an endeavor to collect academic writings in this field and to present them in a comprehensive and orderly manner. It is useful to electrical engineers in industries and postgraduate and graduate students of electrical engineers.

Using a logical and systematical manner, designing and optimizing the full-electronic tap-changer for distribution transformers are carried. The design process is divided into two parts:

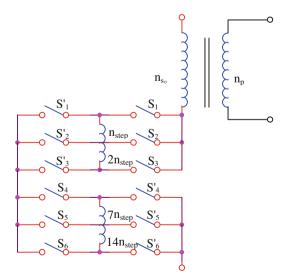

- 1. Designing tapped windings structure and switches configurations (design of power section)

- 2. Designing closed-loop control system

In the power section design of the full-electronic tap-changers a fully new perspective of all possible structures are introduced and categorized comprehensively. Since one of the major barriers in the expanding the application of the full-electronic tap-changer is its high cost, the major factors influencing the cost—number and ratings of the semi-conductor switches and the number of transformer taps—the cost function as an objective function is proposed and the optimal structure is then determined based on this objective function.

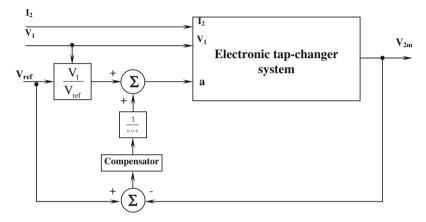

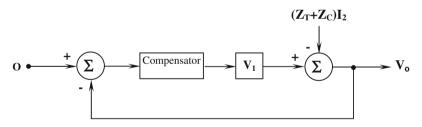

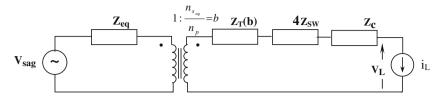

In the control section design, the mechanical tap-changer control system is reviewed; the full electronic tap-changer is modeled and closed-loop control of the full-electronic tap-changer is designed using a new method. In this method, first problem is made less complex by imposing five disciplined assumptions on the design process and design is carried out. These assumptions are then concealed one by one, the necessary modifications are applied in the control system, and the final design is followed.

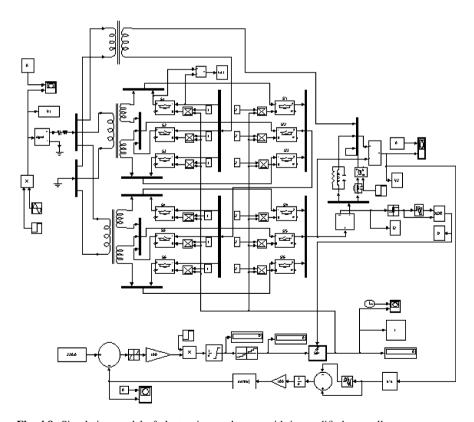

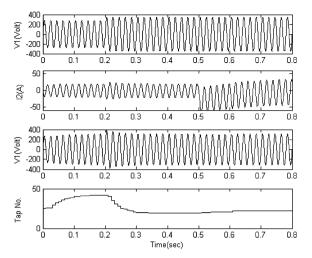

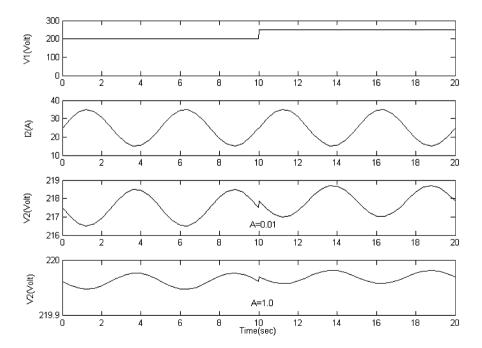

Simulink software is used to simulate the power section of the full-electronic tap-changer with its control section. Simulation results show the correctness of the design procedure. Following the design of the full-electronic tap-changer,

vi Preface

performance and capabilities of this system is investigated for power quality enhancement. It is compared with other custom power tools from economical outlook. Finally, a low-power 5 kW full-electronic tap-changer prototype is built and tested to show the whole design and simulation stages. Experimental results demonstrate the theoretical predictions.

Tehran, January 2011

Jawad Faiz Behzad Siahkolah

### Acknowledgments

This book would never have been possible without the help of a number of peoples and organizations over the last 10 years. We would especially like to thank the University of Tehran for financial support of this work. We would also like to thank Dr. Keyvanpanah, the Assistant Professor of the Department of English Language, Faculty of Foreign Languages of the University of Tehran for editing the text, M.R. Okhovvat for developing the required tap-changer control softwares, Kavandish Company in Tehran, Iran, for helping to build the prototype tap-changer.

## **Contents**

| 1 | Past | and Present                                                | 1   |

|---|------|------------------------------------------------------------|-----|

|   | 1.1  | Introduction                                               | 1   |

|   | 1.2  | Under-Load Tap-Changer                                     | 2   |

|   |      | 1.2.1 Under-Load Reactor Tap-Changers                      | 3   |

|   |      | 1.2.2 Under-Load Resistor Tap-Changers                     | 5   |

|   | 1.3  | Limitations: Mechanical Under-Load Tap-Changers            | 6   |

|   | 1.4  | Electronically Assisted Under-Load Tap-Changers            | 8   |

|   | 1.5  | Full-Electronic Tap-Changers                               | 18  |

|   | 1.6  | The Goal of this Book                                      | 33  |

|   | 1.7  | Future Chapters                                            | 33  |

|   | Refe | rences                                                     | 34  |

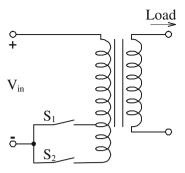

| 2 | Doci | gn of Taps Winding Structure and Configuration of Switches |     |

| 4 |      | ull-Electronic Tap-Changer                                 | 37  |

|   | 2.1  | Introduction                                               | 37  |

|   | 2.1  |                                                            |     |

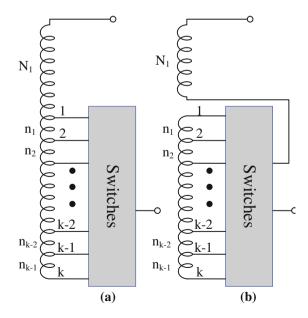

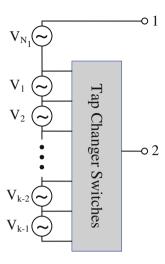

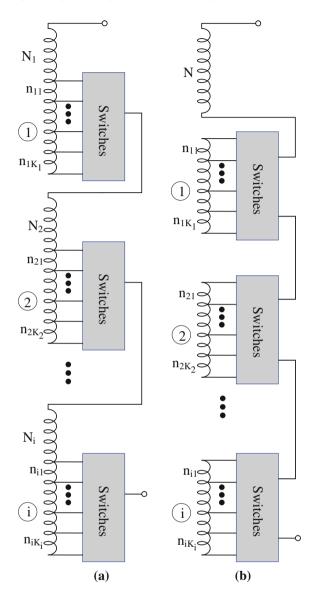

|   |      | The Design of Transformer Taps Configuration               | 38  |

|   | 2.3  | Voltage Selection of Each Part of Windings                 | 4.5 |

|   | 2.4  | in Tapped-Winding                                          | 47  |

|   | 2.4  | Switches Arrangement                                       | 50  |

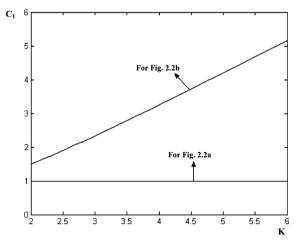

|   | 2.5  | Optimal Topology Exclusive of Influence of Voltage         |     |

|   |      | Amplitude and Switches Currents                            | 55  |

|   | 2.6  | Optimal Topology Considering Impact of Voltages and        |     |

|   |      | Currents of Switches                                       | 58  |

|   | Refe | rences                                                     | 60  |

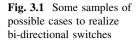

| 3 | Bi-D | Pirectional Solid-State Switches in Full-Electronic        |     |

|   | Tap- | -Changer                                                   | 61  |

|   | 3.1  | Introduction                                               | 61  |

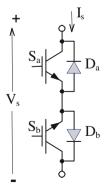

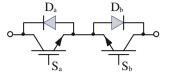

|   | 3.2  | Realization of Bi-Directional Switches                     | 61  |

|   | 3.3  | Switch-On Condition Losses in Bi-Directional Switches      | 63  |

|   | 3.4  | Current Commutation Between Bi-Directional Switches        | 64  |

x Contents

|   | 3.5   | Commi   | utation Based on Current Direction                    | 65  |

|---|-------|---------|-------------------------------------------------------|-----|

|   | 3.6   | Commi   | utation Based on Voltage Amplitude                    | 67  |

|   | 3.7   | Commi   | utation of Current Between Bi-Directional Switches    |     |

|   |       | in Elec | tronic Tap-Changer                                    | 69  |

|   | 3.8   |         | of Snubber Capacitor at Terminal                      |     |

|   |       | of Elec | tronic Tap-Changer                                    | 71  |

|   | 3.9   | Switchi | ing Losses in Bi-Directional Switches                 | 72  |

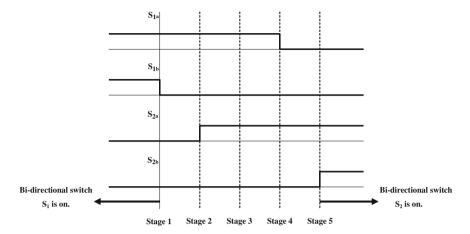

|   | 3.10  | Modula  | ation of Switches in Electronic Tap-Changer           | 74  |

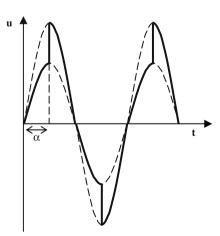

|   |       | 3.10.1  | Phase Control Modulation                              | 75  |

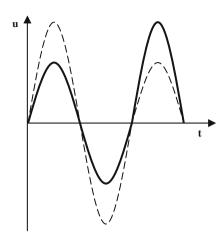

|   |       | 3.10.2  | Discredited Cycle Modulation                          | 75  |

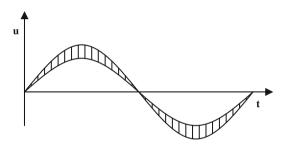

|   |       | 3.10.3  | Pulse Width Modulation                                | 75  |

|   |       | 3.10.4  | No Modulation                                         | 76  |

|   | Refer | ences   |                                                       | 77  |

|   |       |         |                                                       |     |

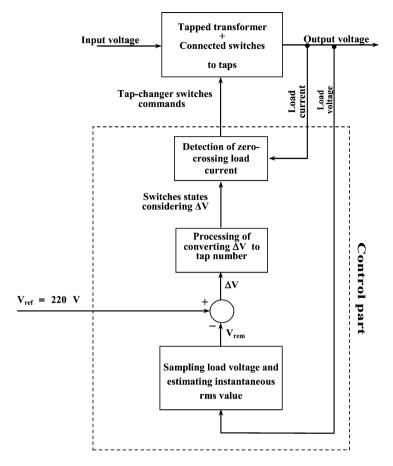

| 4 |       |         | ntroller of Full-Electronic Tap-Changer               |     |

|   |       |         | oltage Regulation                                     | 79  |

|   | 4.1   |         | ction                                                 | 79  |

|   | 4.2   |         | nces of Controller in Mechanical                      |     |

|   |       |         | ectronic Tap-Changers                                 | 80  |

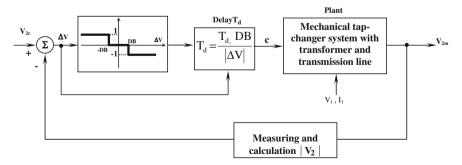

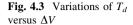

|   | 4.3   |         | ntional Controller in Mechanical Tap-Changers         | 81  |

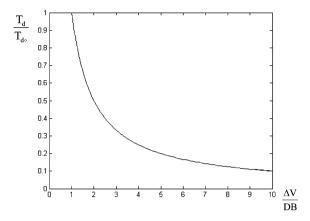

|   | 4.4   |         | cation of Conventional Controller                     |     |

|   |       | for Ele | ctronic Tap-Changer                                   | 83  |

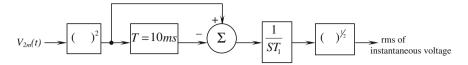

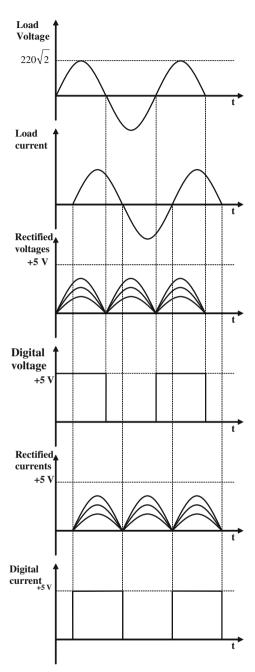

|   |       | 4.4.1   | Changing Block of Measuring and Calculating           |     |

|   |       |         | the rms value to the Block of Measuring and           |     |

|   |       |         | Calculating rms Instantaneous Value                   | 84  |

|   |       | 4.4.2   | Changing DB and Saturation Block to DB Block          | 85  |

|   |       | 4.4.3   | Changing Delay Block to Compensating Block            | 85  |

|   |       | 4.4.4   | Adding a Quantizer Block, Sampling and Storing Block, |     |

|   |       |         | Detecting Zero Crossing Block and Look-Up Table       | 85  |

|   | 4.5   |         | on of Parameters in Modified Controller               | 86  |

|   |       | 4.5.1   | Selection of DB                                       | 86  |

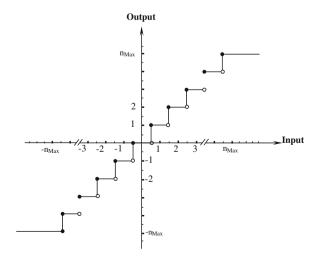

|   |       | 4.5.2   | Selection of Parameters of Quantizer Block            | 87  |

|   |       | 4.5.3   | Selection of Compensator Block                        | 87  |

|   | 4.6   |         | tion of Electronic Tap-Changer                        |     |

|   |       |         | Iodified Controller                                   | 88  |

|   | 4.7   |         | ller Design for Electronic Tap-Changer                | 90  |

|   | 4.8   |         | ude and Phase Measurement of a Sinusoidal             |     |

|   |       |         | le Algorithm                                          | 101 |

|   |       | 4.8.1   | Use of Sinusoidal Variable Peak                       | 102 |

|   |       | 4.8.2   | Evaluation of rms Value of Sinusoidal Variable        | 103 |

|   |       | 4.8.3   | 90° Delay of Sinusoidal Variable                      | 103 |

|   |       | 4.8.4   | Fourier Transformation of Sinusoidal Variable         | 104 |

|   |       | 4.8.5   | Using Phase Locked Loop (PLL)                         | 104 |

|   |       | 4.8.6   | Using Numerical Matrix Method                         | 105 |

Contents xi

|                 | 4.8.7                                                                                                                                 | Comparison Between Proposed Methods and Selection of an Appropriate Method                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Refe            | erences .                                                                                                                             | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Elec            | etronic T                                                                                                                             | ap-Changer as Custom Power Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

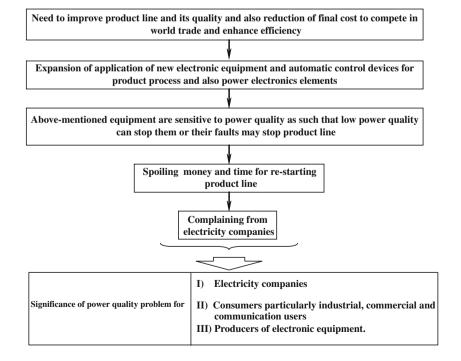

| 5.1             |                                                                                                                                       | round                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                 | 5.1.1                                                                                                                                 | Introduction to Power Quality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                 | 5.1.2                                                                                                                                 | Definition of Power Quality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                 | 5.1.3                                                                                                                                 | Quality of Voltage and Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                 | 5.1.4                                                                                                                                 | Reasons for Importance of Power Quality                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5.2             |                                                                                                                                       | Quality Phenomena                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0.2             | 5.2.1                                                                                                                                 | Classification of Power Quality Phenomena                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                 | 5.2.2                                                                                                                                 | Sag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5.3             |                                                                                                                                       | on for Power Quality Problems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.4             |                                                                                                                                       | Electronic Tap-Changer for Sag Mitigation                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

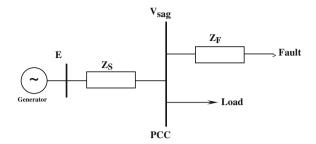

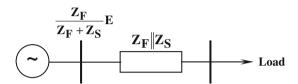

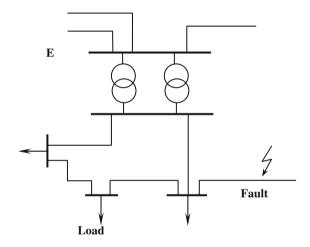

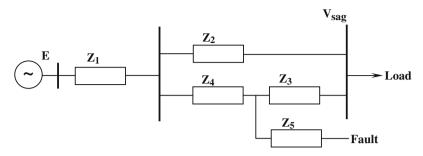

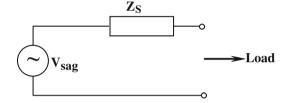

|                 | 5.4.1                                                                                                                                 | Modeling Short-Circuit Fault.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                 | 5.4.2                                                                                                                                 | Compensating Range of Electronic Tap-Changer                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                 | 5.4.3                                                                                                                                 | Comparison of Electronic Tap-Changer and Other                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                 | 0                                                                                                                                     | Sag Mitigation Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                 |                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Refe            | erences .                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Refe            | erences .                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                 | ctical Im                                                                                                                             | plementation and Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

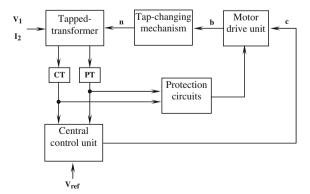

| <b>Pra</b> 6.1  | ctical Im<br>Techni                                                                                                                   | plementation and Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Pra             | <b>ctical Im</b><br>Techni<br>Hardw                                                                                                   | plementation and Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

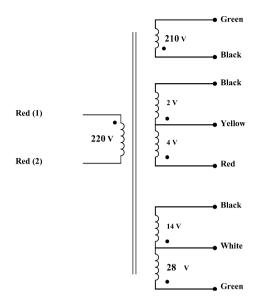

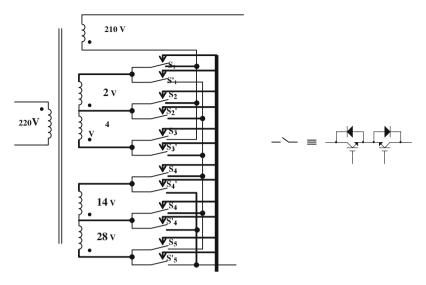

| <b>Pra</b> 6.1  | ctical Im<br>Techni<br>Hardw<br>6.2.1                                                                                                 | plementation and Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

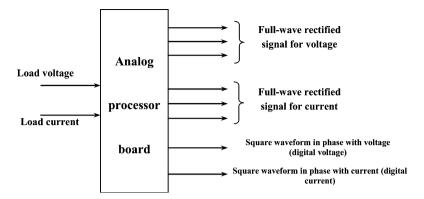

| <b>Pra</b> 6.1  | Techni<br>Hardw<br>6.2.1<br>6.2.2                                                                                                     | plementation and Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| <b>Pra</b> 6.1  | ctical Im<br>Techni<br>Hardw<br>6.2.1                                                                                                 | plementation and Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

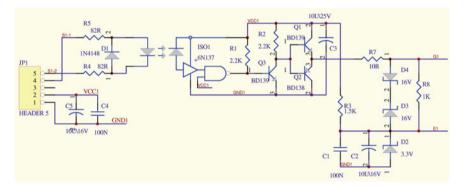

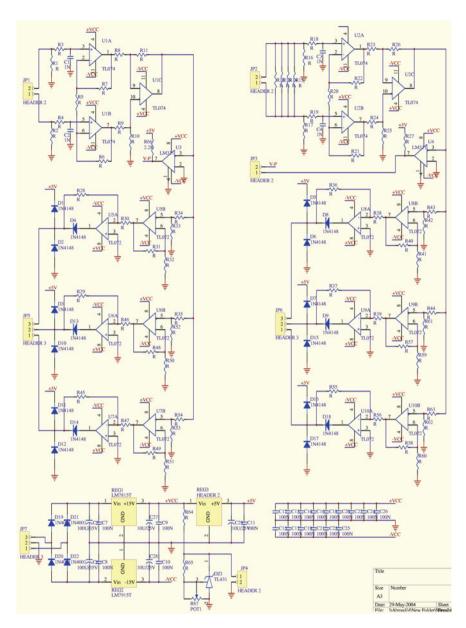

| <b>Pra</b> 6.1  | Techni<br>Hardw<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4                                                                                   | plementation and Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| <b>Pra</b> 6.1  | Techni<br>Hardw<br>6.2.1<br>6.2.2<br>6.2.3                                                                                            | plementation and Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| <b>Pra</b> 6.1  | Techni<br>Hardw<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4                                                                                   | plementation and Experimental Results  cal Specifications and Block Diagram of Prototype are  Tapped-Transformer  Electronic Tap-Changer Switches  Drives of Solid-State Switches  Analogue Processor Board                                                                                                                                                                                                                                                                                                       |

| <b>Pra</b> 6.1  | Techni<br>Hardw<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5                                                                          | plementation and Experimental Results cal Specifications and Block Diagram of Prototype are Tapped-Transformer Electronic Tap-Changer Switches Drives of Solid-State Switches Analogue Processor Board Microprocessor Processing Board                                                                                                                                                                                                                                                                            |

| <b>Pra</b> 6.1  | Techni<br>Hardw<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6<br>6.2.7                                                        | plementation and Experimental Results cal Specifications and Block Diagram of Prototype are Tapped-Transformer Electronic Tap-Changer Switches Drives of Solid-State Switches Analogue Processor Board Microprocessor Processing Board Panel Board                                                                                                                                                                                                                                                                |

| Prac 6.1 6.2    | Techni<br>Hardw<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6<br>6.2.7                                                        | plementation and Experimental Results cal Specifications and Block Diagram of Prototype are Tapped-Transformer Electronic Tap-Changer Switches Drives of Solid-State Switches Analogue Processor Board Microprocessor Processing Board Panel Board PT and CT                                                                                                                                                                                                                                                      |

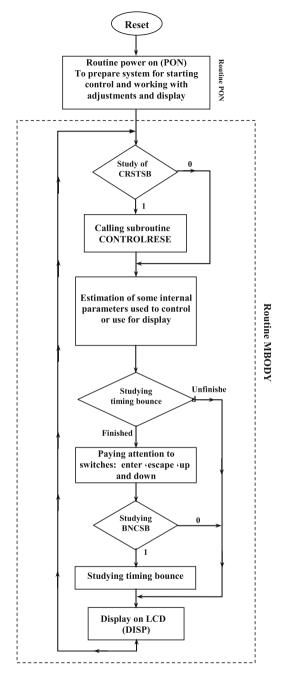

| Prac 6.1 6.2    | Techni<br>Hardw<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6<br>6.2.7<br>Softwa                                              | plementation and Experimental Results cal Specifications and Block Diagram of Prototype are Tapped-Transformer Electronic Tap-Changer Switches Drives of Solid-State Switches Analogue Processor Board Microprocessor Processing Board Panel Board PT and CT                                                                                                                                                                                                                                                      |

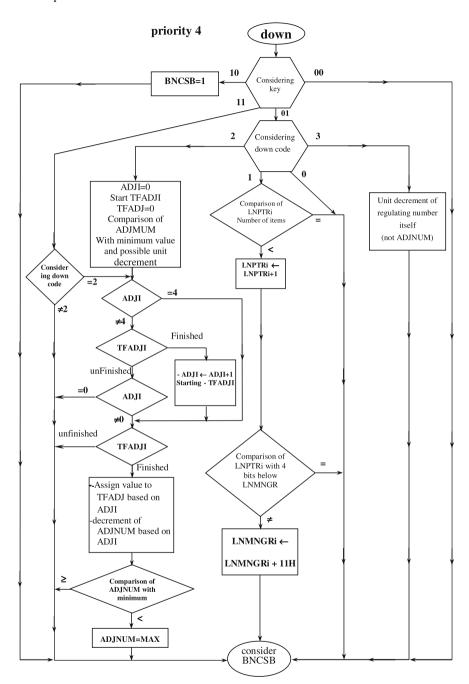

| Prac 6.1 6.2    | Techni<br>Hardw<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6<br>6.2.7<br>Softwa<br>6.3.1                                     | plementation and Experimental Results cal Specifications and Block Diagram of Prototype are Tapped-Transformer Electronic Tap-Changer Switches Drives of Solid-State Switches Analogue Processor Board Microprocessor Processing Board Panel Board PT and CT ure General Strategy of Software Design Main Routine of Program                                                                                                                                                                                      |

| Prac 6.1 6.2    | Techni<br>Hardw<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6<br>6.2.7<br>Softwa<br>6.3.1<br>6.3.2                            | plementation and Experimental Results cal Specifications and Block Diagram of Prototype are Tapped-Transformer Electronic Tap-Changer Switches Drives of Solid-State Switches Analogue Processor Board Microprocessor Processing Board Panel Board PT and CT are General Strategy of Software Design Main Routine of Program Implementation of Control Logic (HIS, HSO, A/D,                                                                                                                                      |

| Prac 6.1 6.2    | Techni<br>Hardw<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6<br>6.2.7<br>Softwa<br>6.3.1<br>6.3.2                            | plementation and Experimental Results cal Specifications and Block Diagram of Prototype are Tapped-Transformer Electronic Tap-Changer Switches Drives of Solid-State Switches Analogue Processor Board Microprocessor Processing Board Panel Board PT and CT are General Strategy of Software Design Main Routine of Program Implementation of Control Logic (HIS, HSO, A/D, Timer 1 and Timer 2).                                                                                                                |

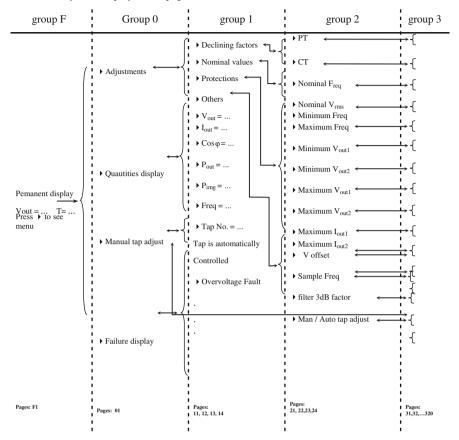

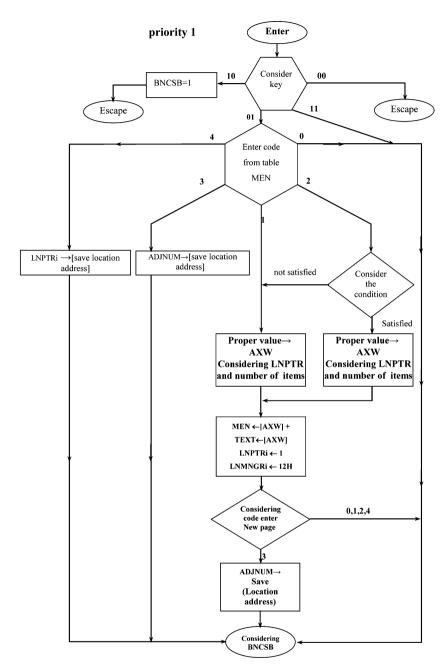

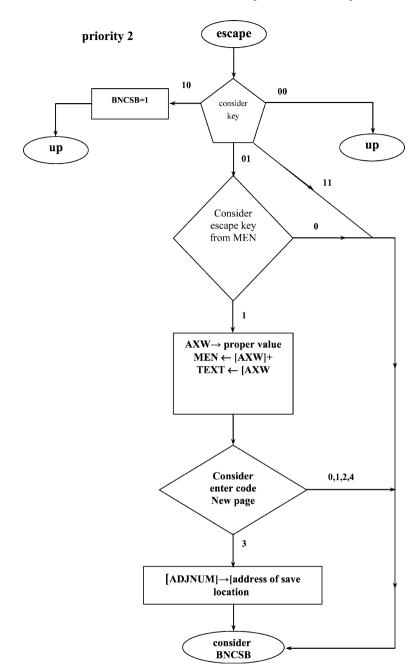

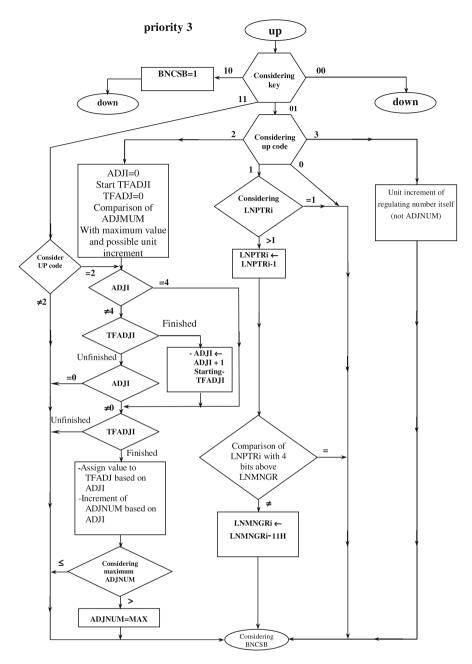

| Prac 6.1 6.2    | Techni<br>Hardw<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6<br>6.2.7<br>Softwa<br>6.3.1<br>6.3.2<br>6.3.3                   | plementation and Experimental Results cal Specifications and Block Diagram of Prototype are Tapped-Transformer Electronic Tap-Changer Switches Drives of Solid-State Switches Analogue Processor Board Microprocessor Processing Board Panel Board PT and CT are General Strategy of Software Design Main Routine of Program Implementation of Control Logic (HIS, HSO, A/D, Timer 1 and Timer 2). Display and Regulations of System                                                                              |

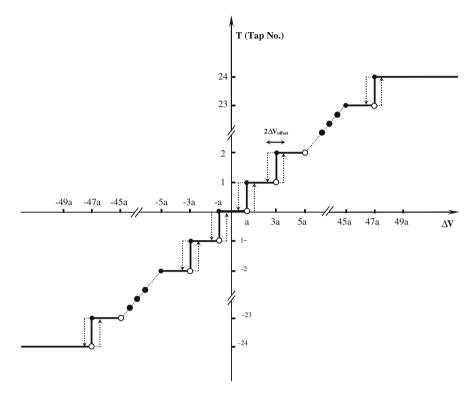

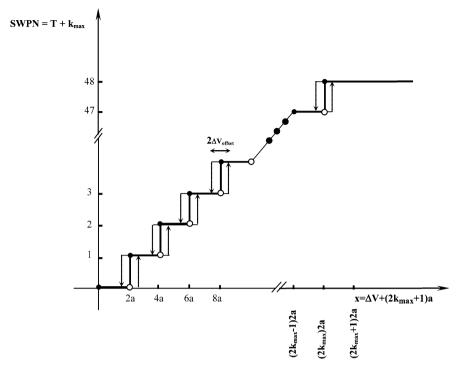

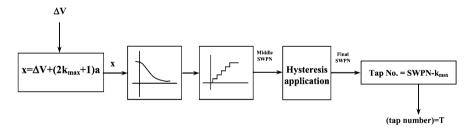

| Prac 6.1 6.2    | Techni<br>Hardw<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6<br>6.2.7<br>Softwa<br>6.3.1<br>6.3.2<br>6.3.3                   | plementation and Experimental Results cal Specifications and Block Diagram of Prototype are Tapped-Transformer Electronic Tap-Changer Switches Drives of Solid-State Switches Analogue Processor Board Microprocessor Processing Board Panel Board PT and CT are General Strategy of Software Design Main Routine of Program Implementation of Control Logic (HIS, HSO, A/D, Timer 1 and Timer 2). Display and Regulations of System Process of Converting \( \Delta V \) into Tap Number                         |

| Pra 6.1 6.2 6.3 | Techni<br>Hardw<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6<br>6.2.7<br>Softwa<br>6.3.1<br>6.3.2<br>6.3.3                   | plementation and Experimental Results cal Specifications and Block Diagram of Prototype are  Tapped-Transformer Electronic Tap-Changer Switches Drives of Solid-State Switches Analogue Processor Board Microprocessor Processing Board Panel Board PT and CT  THE  General Strategy of Software Design Main Routine of Program Implementation of Control Logic (HIS, HSO, A/D, Timer 1 and Timer 2). Display and Regulations of System Process of Converting $\Delta V$ into Tap Number and Keys Commands        |

| Prac 6.1 6.2    | Techni<br>Hardw<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6<br>6.2.7<br>Softwa<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>6.3.5 | plementation and Experimental Results cal Specifications and Block Diagram of Prototype are  Tapped-Transformer Electronic Tap-Changer Switches Drives of Solid-State Switches Analogue Processor Board Microprocessor Processing Board Panel Board PT and CT  are  General Strategy of Software Design Main Routine of Program Implementation of Control Logic (HIS, HSO, A/D, Timer 1 and Timer 2). Display and Regulations of System Process of Converting ΔV into Tap Number and Keys Commands mental Results |

| Pra 6.1 6.2 6.3 | Techni<br>Hardw<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6<br>6.2.7<br>Softwa<br>6.3.1<br>6.3.2<br>6.3.3                   | plementation and Experimental Results cal Specifications and Block Diagram of Prototype are  Tapped-Transformer Electronic Tap-Changer Switches Drives of Solid-State Switches Analogue Processor Board Microprocessor Processing Board Panel Board PT and CT  THE  General Strategy of Software Design Main Routine of Program Implementation of Control Logic (HIS, HSO, A/D, Timer 1 and Timer 2). Display and Regulations of System Process of Converting $\Delta V$ into Tap Number and Keys Commands        |

| xii | Contents |

|-----|----------|

| 7 | Conc  | lusions and Suggestions | 171 |

|---|-------|-------------------------|-----|

|   | 7.1   | Conclusion              | 171 |

|   | 7.2   | Suggestions             | 182 |

|   | Refer | rences                  | 183 |

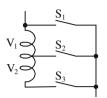

# Chapter 1 Past and Present

### 1.1 Introduction

Distribution transformer tap is a connection which is taken out from a node located between two ends of a winding [1]. This permits changes in voltage, current or turns ratio of the transformer after it has left the factory. The reasons to have a series of taps in the transformer are as follows [2]:

- a. To fix the secondary voltage against the primary voltage changes;

- b. To change the secondary voltage;

- c. To provide an auxiliary secondary voltage for a specific application such as lighting;

- d. To reduce voltage for starting rotating motors;

- e. To provide a natural point for earthing or conducting unbalanced current in three-wire single-phase circuits or four-wire three-phase circuits.

In the transformers used in power systems the main reason for taps application is adjusting and controlling the voltage [3]. The load fluctuations change the voltage of the power system. It is noted that sometimes taps in power transformers are used to shift the phase angle [4, 5].

Tap-changers are categorized into two main groups [6]:

- a. Off-circuit or no-load tap-changers;

- b. On-load or under-load tap-changers.

Tap-changer with the ability to change taps while power is on called under-load tap-changer. If a tap-changer is built as such that its fixing requires its being disconnected from the power line, the tap-changer is called no-load tap-changer.

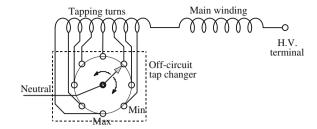

If there is a need to change the turns ratio over a long interval (for instance seasonal), the no-load tap-changer is used. Normally in the no-load tap-changers taps are changed manually by means of a selector outside the transformer tank. This selector may move linearly or circularly [2]. Figure 1.1 presents the structure

**Fig. 1.1** Structure of an no-load tap-changer [7]

of a no-load tap-changer with a circular selector. For short intervals (different hours of day), it is not possible to disconnect the transformer from the power system and therefore under-load tap-changers must be used to change the taps. This type of tap-changer is widely used in power systems and their details are presented in the following parts.

### 1.2 Under-Load Tap-Changer

Before establishing large and wide transmission power networks, the common technique for voltage adjustment in small and isolated networks was the use of a generator. This voltage adjustment was done through by generator excitation system [8]. However, the voltage of different parts of a large network cannot be adjusted using such a technique. In larger networks an on-load tap-changer must be used in order to adjust the under-load voltage continuously. These tap-changers are fixed on the transmission transformers and also the main load supplying transformers in order to compensate voltage changes which are caused by load fluctuations [4].

The structure of under-load tap-changers is more complex than that of the no-load version. There are two basic features shared by all under-load tap-changer [2, 9, 10].

- a. During tap changing stages, taps are never short-circuited; thus an impedance is used to prevent the short-circuit.

- b. Load is not disconnected during tap-changing process. To this ends, there is typically a two-element circuit in the under-load tap-changer, when switching and tap changing are carried out in one element of the circuit, the load current continues to pass in the other element.

The impedance used in under-load tap-changers is a tapped resistor or inductor and so it is called resistor or inductor tap-changer. Although the advantage of resistors because of their short time duration and consequently longer life of contacts was already known, the earlier designs of tap-changers followed the tapped inductor version. The reason for the wide spread use of tapped-inductor under-load tap-changers was its ability to continuously pass the load current; while resistors (based on their rating) can pass the load current over a very short period of time. The absence this feature is the possible damage of the moving mechanical system of the tap-changers which stops the tap-changers operation, while the load

current passes the tap-changer impedance. As mechanical systems used in the under-load tap-changers became advanced inductor tap-changers have gradually been replaced by resistor tap-changers [2].

### 1.2.1 Under-Load Reactor Tap-Changers

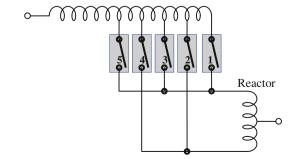

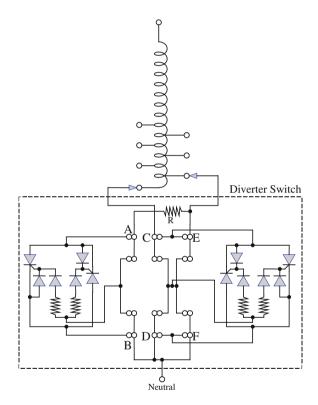

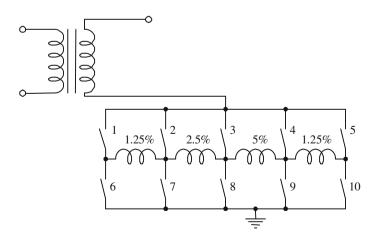

The reactor under-load tap-changer was invented in 1926 [5]. There are different circuits as used in this tap-changer. Figure 1.2 shows the simplest form of an under-load reactor tap-changer in which an under-load switch is connected to each tap. The under-load switch is a switch which can be turned on and off under load.

According to Fig. 1.2, the switches are connected to each other alternatively and form two distinctive groups. Each group is connected to a terminal of the reactor. Table 1.1 summarizes various positions of the tap-changer based on the different conditions of the switches.

According to Table 1.1, only switch no. 1 at position 1 is on and the current passes only an half of the reactor. In order to transfer the tap to position no. 2, in addition to switch no. 1, switch no. 2 will be on. In this case the reactor is placed between tap no. 1 and tap no. 2 and prevents the short circuit of the taps. Meanwhile, the load current continues through the middle terminal of the reactor, and the load voltage is the mean voltage of tap no. 1 and tap no. 2. Therefore, in this configuration we can conveniently get the taps mid-voltage and this is one of the advantages of this structure. To change the position to position no. 3, switch no. 1 is off and only switch no. 2 is on; in this case the second half of the reactor will be the load current path.

Similarly, tap changing to further positions are possible based on Table 1.1.

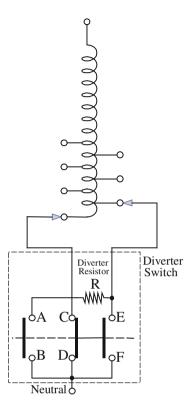

There are (2n-1) positions for the load voltage in the tap-changer of Fig. 1.2 (n is the number of taps) and this is an advantage. However, the number of underload switches is equal to the number of taps and this increases the volume, cost and complexity of the system. Figure 1.3 presents an alternative under-load tap-changer in which there are two off-load selector switches to select the tap and only two under-load switches (diverter switch) exist for diverting the load current during tap-changing stage [2].

**Fig. 1.2** The simplest form of an under-load reactor tap-changer [2]

|                         |    | 0 1 |    | ` U | /  |    |    |    |    |

|-------------------------|----|-----|----|-----|----|----|----|----|----|

| Switch no./position no. | 1  | 2   | 3  | 4   | 5  | 6  | 7  | 8  | 9  |

| 1                       | ON | ON  |    |     |    |    |    |    |    |

| 2                       |    | ON  | ON | ON  |    |    |    |    |    |

| 3                       |    |     |    | ON  | ON | ON |    |    |    |

| 4                       |    |     |    |     |    | ON | ON | ON |    |

| 5                       |    |     |    |     |    |    |    | ON | ON |

|                         |    |     |    |     |    |    |    |    |    |

**Table 1.1** Stages of tap changing in tap-changer (Fig. 1.2)

Selector switches and diverter switches are coupled with the gears of tapchanging mechanical system. In this tap-changer, taps are changed in the following ways:

- a. Diverter switch no. 1 is opened.

- b. Selector switch no. 1 moves.

- c. Diverter switch no. 1 is reclosed.

- d. Diverter switch no. 2 is opened.

- e. Selector switch no. 2 moves.

- f. Diverter switch no. 2 is reclosed.

One other advantages of the tap-changer in Fig. 1.3 is that the voltage drop on the reactor is zero, except at the tap-changing time. The inductance must not be very large in order to decrease the voltage drop, but must be very small in order to increase the rotating current between the adjacent tapes during tap-changing stages.

As already mentioned, the main advantage of under-load reactor tap-changers is that the reactor stands the continuous load current, so if the moving mechanical system for the tap-changer is damaged and stopped during the tap-changing process, the tap-changer will not burn and transformer will not fail. On the other hand, under-load reactor tap-changers have also some drawbacks, such as low changing speed, long arcs during tap-changing, short life of contacts and large volume of reactors. This is the reason that the use of these tap-changers has become obsolete. However, some improvements have been made in their structure and they are used in North America

**Fig. 1.3** Under-load reactor tap-changer with two underload switches [2]

### 1.2.2 Under-Load Resistor Tap-Changers

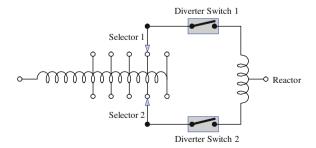

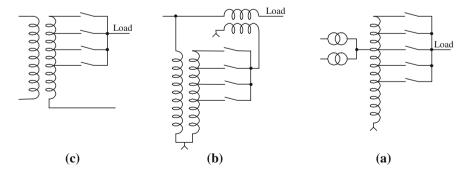

Under-load reactor tap-changers have been almost totally replaced by fast under-load resistor tap-changers. Generally two basic circuit arrangements have been used in resistor tap-changers [2]:

- a. Those which do tap selection and load current deviation in one single contact (type I).

- b. Those which have distinctive diverter switches and tap selection switches (type II).

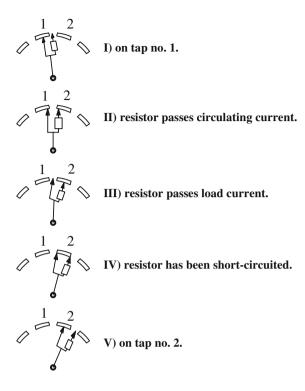

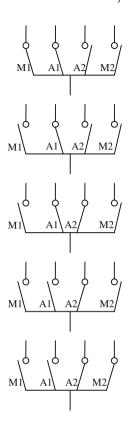

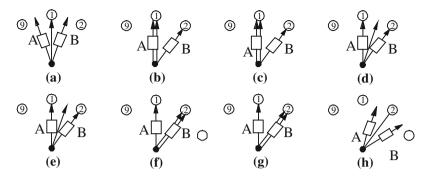

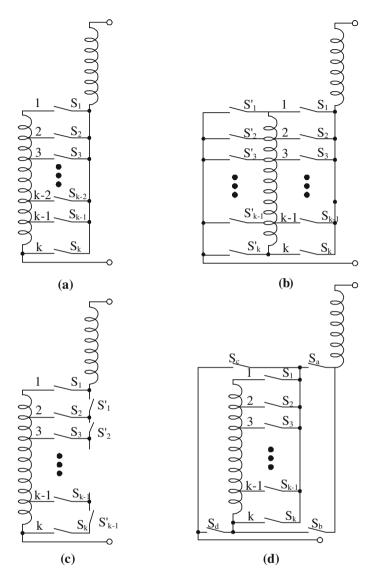

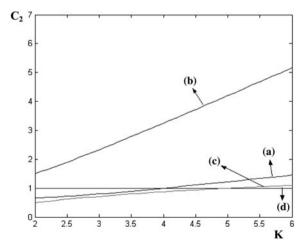

Figure 1.4 shows the different circuit arrangements of switches in the resistor tap-changers and Fig. 1.4a the type I arrangement. Such an arrangement is normally done by rotating switches and is called Pennant cycle. Figure 1.5 shows the stages of tap changing in this type of tap-changer. Figure 1.4b-d present the type II arrangements. In these figures the arrangement of the selector switches, similar to the diverter switches, differ from the type I arrangement. These arrangements are called the Flag cycle.

In large transformers the arrangement type II are normally used. Figure 1.6 presents the stages of tap-changing in Fig. 1.4d structure.

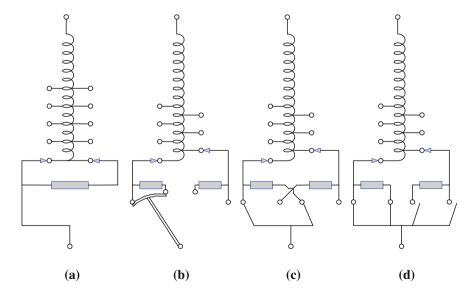

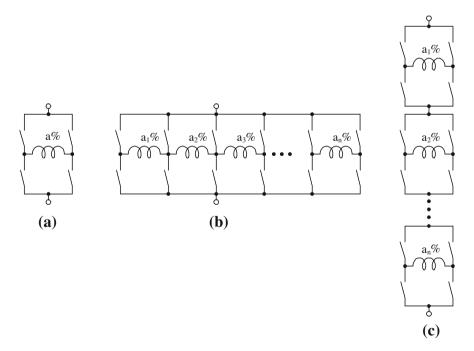

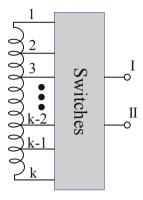

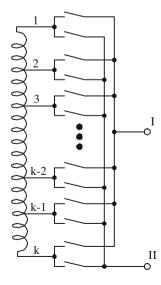

There are different structures for selector switches and transformer taps. Figure 1.7 shows three types of these structures [11].

Figure 1.7a shows a structure in which the taps are placed in linear steps. When the range of taps is wide, the structures of Fig. 1.7b and c can be use, in order to reduce the number of taps and their voltage between any one tap and the next. Structure of Fig. 1.7b shows a condition in which the taps winding can be inversed and, therefore, it will be possible to add to or subtract from the taps winding voltage from the main winding.

Fig. 1.4 Different arrangements of switches in resistor tap-changers

**Fig. 1.5** Stages of tapchanging from tap number 1 to tap number 2 in the arrangement (Fig. 1.4a)

For precise adjustment, there are two types of taps: the taps with large steps and taps with small steps.

### 1.3 Limitations: Mechanical Under-Load Tap-Changers

In spite of advancement in the structure of mechanical under-load tap-changers, these tap-changers have some drawbacks; for example, the major factor which causes damage to power transformers is their tap-changer failure [12]. Some drawbacks of mechanical under-load tap-changers are as follows [13].

a. Contact Arc in Diverter Switches During Tap-Changing Process An arc appears in the contacts of diverter switches at the time of make and breaks the load current. This arc causes impurity of the oil surrounding the diverter switches and wearing out of the contacts of the switches.

### b. High Maintenance and Service Cost

Conditions of oil, contacts and mechanical parts of the mechanical under-load tapchangers must be inspected regularly. This is required due to arc and wearing-out of the moving mechanical parts of tap-changer.

**Fig. 1.6** Stages of tapchanging in structure (Fig. 1.4d) [2]

Fig. 1.7 Different structures for taps of selector switches in under-load resistor tap-changer [11]

### c. Low Speed of Tap-Changing

The low speed of tap-changing originates from mechanical nature of tap-changing process and the required time for storing the desirable energy for tap-changing process. In an under-load resistor tap-changer, it takes 100 s to change tap number 1 to tap number 19 [14].

d. High Losses of Tap-Changer During Tap-Changing

This happens for under-load resistor tap-changer and reason is the use of passing resistors in this type of tap-changer.

In order to remove the above-mentioned limitations and drawbacks, the following new circuits and structures have been suggested for under-load tap-changers [15]. These are categorized into two major groups [15, 16].

a. Electronically Assisted Under-Load Tap-Changers (or Hybrid On-Load Tap-Changer)

In these tap-changers solid-state power switches have been used beside the mechanical switches in order to reduce the arc caused by tap-changing. Mechanical parts of the conventional under-load tap-changer systems have been still used.

b. Fully Electronic Under-Load Tap-Changer (or Solid-State Under-Load Tap-Changer or Static On-Load Tap-Changer)

There is no moving mechanical part in fully electronic tap-changers and whole tap-changer has been built by solid-state power switches. In Sects. 1.4 and 1.5, both groups are described and their drawbacks and advantages are given.

### 1.4 Electronically Assisted Under-Load Tap-Changers

One of the most important problems of mechanical under-load tap-changers is the arc in the contacts of diverter switches during the tap-changing process. The reason for appearance of arc is the mechanical nature of the switches. Of course, mechanical switches are interesting in the connecting of instant due to a very low voltage, however during tap-changing it has arc.

The main idea in the use of fully electronic under-load tap-changer is that during tap-changing process solid-state power switches with more controllability compared with the mechanical switches, come in and reduce the arc. But in a fixed tap, solid-state power switches exit the circuit and mechanical switches pass the load current. The reason is a very low connection voltage of mechanical switches compared with the solid-state power switches.

The first suggested circuit for the hybrid tap-changers is shown in Fig. 1.8. Figure 1.8 also presents the tap-changer diverter switches. The tap-changing switches in this structure do not differ from the under-load resistor tap-changer. In fact, Fig. 1.8 is the improved version of the under-load resistor tap-changer

Fig. 1.8 First suggested circuit for hybrid tapchangers [17]

in Fig. 1.4b. In the structure shown in Fig. 1.8 (similar with the structure of Fig. 1.4b), in order to change the tap, the moving contact  $C_5$  must move from left to right (or from right to left). However, in the structure of Fig. 1.8, before isolating  $C_5$  from any of the fixed contacts, or connecting it to any of the fixed contacts, the relevant thyristors in Fig. 1.8 are turned-on and, therefore, no arc is caused. For example, at the moment of isolating contact  $C_5$  from contact  $C_1$ , already a pair thyristors (1) has been turned-on and at the moment of isolating contact  $C_5$  from  $C_1$  by deviating the current from contact  $C_1$  to a pair thyristors (1), the arc is minimized. The pair thyristors (1) is turned-off at the first crossing zero-current and the load current is transferred to resistor  $R_1$ . This happens before contact  $C_5$  approaches contact  $C_3$ . Therefore, the time between isolating contact  $C_5$  from  $C_1$  and approaching contact  $C_3$  is longer than an half cycle and this can already turned-off the pair thyristors (1). Pair thyristors (2) is turned-on before contact  $C_5$  approaches  $C_2$  and this does not allow an arc to be appeared as  $C_5$  connects to  $C_3$ .

The structure suggested in Fig. 1.8 can largely reduce the arc, but its weakness is that although in this structure the pair thyristors are turned-on over a short time during tap-changing process, they are permanently connected to the diverting switches circuit and reduce the reliability of the system due to a possible burning of the thyristors. To solve this problem, the structure shown in Fig. 1.9 is recommended [18].

The main idea of this structure is that the pair thyristors are connected to the circuit only during tap-changing and in other instants it must be isolated from the circuit. In this case the tap-changer system does not fail if the thyristors burn and this increases the reliability of the system. To better explain the operation of the tap-changer of Fig. 1.9, first the contacts positions are described in the structure of Fig. 1.10 during switch-on and off periods.

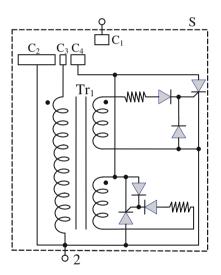

Switch S between terminals 1 and 2 in Fig. 1.10 consists of fixed contact  $C_1$  and main moving contact of  $C_2$ . In this structure, sensing contact  $C_3$  and auxiliary contact  $C_4$  have been included to reduce the arc. Auxiliary contact  $C_4$  has been connected to terminal 2 through a pair thyristors and sensing contact  $C_3$  has been connected to a pulse transformer primary  $Tr_1$  terminal. Secondary of this transformer has been connected to the thyristors gate through a resistor and a diode. Contacts  $C_2$ ,  $C_3$  and  $C_4$  are movable and connected mechanically to each others, but they are isolated electrically.

Fig. 1.9 Hybrid tap-changer structure [18]

**Fig. 1.10** Contacts positions in suggested tap-changer of Fig. 1.9

To connect switch S, contacts  $C_2$ ,  $C_3$  and  $C_4$  move from left to right. Stages of connecting switch S are as follows:

- a. Movable contacts  $C_2$ ,  $C_3$  and  $C_4$  move to left and auxiliary contact  $C_4$  connects to fixed contact  $C_1$ . Since in this case thyristors gates commands have not been issued, there is no current between terminals 1 and 2 of switch S and voltage difference between terminals 1 and 2 is applied to the pair thyristors.

- b. By continuation of moving the movable contacts to the left, in addition to auxiliary contact  $C_1$ , sensing contact  $C_3$  is also connected to fixed contact  $C_1$ . Therefore, two terminals of the primary of the transformer  $Tr_1$  is short-circuited

and thyristors gates commands are disconnected. So the thyristors are switched-off the first zero load current crossing and the total current is transferred to contact  $C_2$ . After full transferring the current to contact  $C_2$ , contacts  $C_3$  and  $C_4$  are isolated from fixed contact  $C_1$ . Thus the process of connecting switch S is terminated.

Paying attention to the process of connecting switch S as described above, it is clear that at the instant of connecting or disconnecting movable contacts  $C_2$ ,  $C_3$  and  $C_4$  from fixed contact  $C_1$  in this process, these contacts do not carry current and therefore the arc reduces largely.

To disconnect switch S, movable contacts must move from right to left. Stages of disconnecting switch S are as follows:

- a. By moving movable contacts C<sub>3</sub> and C<sub>4</sub> to the right, in addition to main contact C<sub>2</sub> that previously connected to fixed contact C<sub>1</sub>, sensing and auxiliary contacts C<sub>3</sub> and C<sub>4</sub> are connected to contact C<sub>1</sub>. However, primary of transformer Tr<sub>1</sub> has no voltage and pair thyristors in this case are off.

- b. By continuation of moving the movable contacts to the left, there is an instant that main contact  $C_2$  is isolating from fixed contact  $C_1$ . In this case contacts  $C_3$  and  $C_4$  connect to contact  $C_1$ . By isolating contact  $C_2$  from contact  $C_1$ , there is a voltage difference between these two contacts that can generate arc. But before the extension of the arc, this voltage difference is applied to the primary of transformer  $Tr_1$  and triggers the gate of one of pair thyristors, and the relevant thyristor is switched-on and transfers the current from contact  $C_1$  to contact  $C_4$ . Therefore, the arc at the instant of isolating contact  $C_1$  and  $C_2$  is extinguished.

- c. By continuation of moving the movable contacts to the right, sensing contact  $C_3$  is isolated from fixed contact  $C_1$  and thus the gate command of thyristors is switched-off and the thyristors will be off at the first zero current crossing and current of switch S is disconnected. After full disconnection of the current, contact  $C_1$  is also isolated from contact  $C_1$  and disconnecting process of switch S is ended.

Considering the above explanations about procedure for on and off of current of switch S in Fig. 1.10, operation of hybrid tap-changer Fig. 1.9 is clear. In this configuration, there are auxiliary and sensing contacts on two sides of the main moveable contact. While the main moveable contact moves to change tap from the left to right, auxiliary and sensing contacts at the left side of this main contact, improves the switching conditions in the switch-off instants of the main contact from the fixed contacts; auxiliary and sensing contacts at the right side of the main contact improves the switching conditions at the switch-on instants of the main contact from the fixed contacts. Therefore, the process of tap-changing in this tap-changer is done with a minimum arc.

Although in the suggested structure of Fig. 1.9 the arc is extinguished well and there will be no high maintenance costs, the tap-changing is still slow due to the use of a mechanical switched structure similar with an under-load resistor

**Fig. 1.11** Alternative hybrid tap-changer [19]

**Fig. 1.12** Connecting pair-thyristor to the mechanical switches for terminal AB [19]

tap-changer (Fig. 1.4b). Meanwhile, the arrangement of the moveable contact in this configuration is complex.

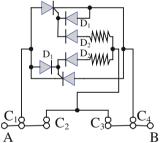

The current disconnection in the switch in Fig. 1.12 is as follows:

An alternative structure, having different deviation switches in which only one transient resistor has been used, is shown in Fig. 1.11 [19]. An auxiliary pair-thyristor has been placed on each moveable contact which switch on terminals AB, CD and EF. Auxiliary pair-thyristor in Fig. 1.11 has not been presented in Fig. 1.12. Figure 1.12 shows the procedure for connecting pair-thyristor to the mechanical switches for terminal AB. The same is also true for other terminals. According to Fig. 1.12, contacts  $C_1$ ,  $C_2$ ,  $C_3$  and  $C_4$  are the mechanical contacts

between terminals A and B. In this system, pair-contact  $(C_1, C_4)$  and also pair-contact  $(C_2, C_3)$  are always turned-on and off simultaneously. Contacts  $C_2$  and  $C_3$  are the main and permanent path of the current, while contacts  $C_1$  and  $C_4$  provide a current auxiliary path at the on and off instants through the pair-thyristor.

The current disconnection sequence in the switch of Fig. 1.12 is as follows:

- a. In the steady-state, current passes contacts  $C_2$  and  $C_3$  as contacts  $C_1$  and  $C_4$  are open. To disconnect the current between terminals A and B, first contacts  $C_1$  and  $C_4$  are closed. There is no gate command in the pair-thyristor and thyristors are off due to zero voltage difference between contacts  $C_1$  and  $C_2$  and also contacts  $C_3$  and  $C_4$ .

- b. Contacts  $C_2$  and  $C_3$  start to open and at the same time, the voltage difference between these contacts and contacts  $C_1$  and  $C_4$  cause arc. Before that, this voltage difference triggers one of auxiliary pair-thyristor and the current transfers to contacts  $C_1$  and  $C_4$  and therefore the arc at contacts  $C_2$  and  $C_3$  extinguished. At the first zero passing, thyristor is switched-off and current is totally off, contacts  $C_1$  and  $C_4$  are also isolated. To ensure the zero current crossing and thyristor switching-off before opening contacts  $C_1$  and  $C_4$ , the time between opening contacts  $C_1$ — $C_3$  and contacts  $C_1$ — $C_4$  must be at least a half-cycle.

Process of passing the current is as follows:

- a. First contacts  $C_1$  and  $C_4$  are connected. However, the gate command of the auxiliary thyristors has not been yet issued, and these thyristors will be off and there will be no current.

- b. In the next stage, contacts  $C_2$  and  $C_3$  start to close. Once an arc is generated in the mentioned contacts due to voltage difference, auxiliary thyristors gate command is issued and current passes through contacts  $C_1$ ,  $C_4$  and auxiliary thyristor, and, therefore, the arc is distinguished.

- c. After full connection of contacts  $C_2$  and  $C_3$ , there will be no gate command for the auxiliary thyristors and in the first crossing the zero, they move to the off mode and whole current will pass through contacts  $C_2$  and  $C_3$ . At this point, contacts  $C_1$  and  $C_4$  will open and then the current will stop.

It is now clear how hybrid tap-changer in Fig. 1.11 operates. The stages of tap-changing are summarized in Table 1.2.

From Table 1.2 it is clear that in a moving stages both contacts CD and EF do not change simultaneously, therefore, a pair-thyristor can be used for each of these contacts. Such configuration has been shown in Fig. 1.13.

Configurations that have been so far suggested can extinguish the arc well, but the tap-changing will be still slow. The reason for this slow tap-changing is the use of conventional mechanical structures of the switches. To enhance the tap-changing speed, the configuration of Fig. 1.14 can be suggested [20], where selector switches and diverter switches have been improved. The selector switches are similar with that of the under-load resistor tap-changer from circuit arrangement point of view, however vacuum switch with a two-state control

**Table 1.2** Stages of tap-changing in Fig. 1.11

|             | AB            | CD | EF |

|-------------|---------------|----|----|

| (a) Passing | left to right |    |    |

| 0           |               | *  |    |

| 1           | *             | *  |    |

| 2           | *             |    |    |

| 3           | *             |    | *  |

| (b) Passing | right to left |    |    |

| 0           | *             |    | *  |

| 1           | *             |    |    |

| 2           | *             | *  |    |

| 3           |               | *  |    |

**Fig. 1.13** A full structure of tap-changer with two auxiliary pair-thyristor [19]

electromechanical actuator is used in the place of contacts within oil and their complex mechanical drive.

Vacuum switches can be used in high voltage power systems. These switches have a long life. They have two windings and are turned-on and turned-off by excitation of the windings. The c hanging time of the vacuum switches from turn-on to turn-off or vice versa is about 20 ms.

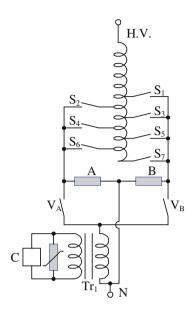

**Fig. 1.14** Configuration of a hybrid tap-changer [20]

Diverter switches in the suggested configuration consist of two solid-state power switches A and B, and two vacuum switches  $V_A$  and  $V_B$ . To transfer the current from the vacuum switches to the solid-state switches, an auxiliary diverter switches circuit in series with vacuum switches  $V_A$  and  $V_B$  is used. The diverter circuit consists of a low power step-up transformer, solid-state power switch C and a varistor (for voltage drop). The solid-state power switches in this configuration are constructed using the switches that can be turned-off through the gate. The tapchanging stages in this configuration are as follows (as an examples the change from tap 2 to tap 3 stages is discussed):

- a. When tap-changer is placed on tap 2, selector vacuum switch, deviation vacuum switch  $V_A$  and solid-state switches C are on and other switches are off. To change tap number 2 to tap number 3, first vacuum selector switch is closed, but no current will pass it.

- b. In crossing zero current, solid-state switch A is on and solid-state switch C is turn-off. By turning-off switch C, the impedance of the current path through vacuum switch  $V_A$  increases and transfers the current to solid-state switch A. The transfer of the current from vacuum switch  $V_A$  to solid-state switch A takes a few ms. Following full transferring the current to solid-state switch A, vacuum switch  $V_A$  is off at zero current.

- c. During crossing the next zero current, solid-state switch A is turn-off and at the same time solid-state switch B is turn-on. Following this, the current transfers to solid-state switch B and vacuum switch  $S_3$ .

- d. Vacuum switch  $V_B$  is on, but the current passing through  $V_A$  and  $V_B$  has high impedance because solid-state switch C is turn-off, and there is no current in  $V_B$ .

e. During crossing the next zero current, solid-state switch B is switched-off and solid-state switch C is off simultaneously. Therefore, current is transferred to solid-state switch V<sub>B</sub>. Finally selector switch S<sub>2</sub> is off and tap-changing stages is ended.

As discussed above, it is clear that in this configuration there is no crossing impedance and in fact during crossing zero current the current is transferred from the even number taps (left hand side number taps) to the odd taps (right side taps) using solid-state switches A and B. This is the reason that jump in tap-changing is possible and each even number tap can jump to any odd number tap and vice versa. The only limiting factor in taps jumping is the peak permissible voltage on the diverter switches.

In the proposed configuration in addition to extinguishing the arc, the tap-changing speed also rises. The required time for tap-changing from tap 1 to tap 19 is about 1.5 s. This is the case if the jumping possibility is not used. In the case, 3 jumps in taps takes shorter time, that is 0.5 s. Of course, in this case voltage of solid-state switches will increase. This is much shorter than 100 s of the under-load resistor tap-changer. One of the other advantages of configuration (Fig. 1.14) is that it gets rid of its complex mechanical system and replaces the vacuum switches. This enhances the mechanical reliability of the system. The reasons are a lower number of components in a vacuum switch and higher reliability. Of course, this configuration has some drawbacks. A higher cost due to the use of several vacuum switches and the permanent connection of the solid-state switches to the tap-changer and, therefore, low electrical reliability are the disadvantages of this system.

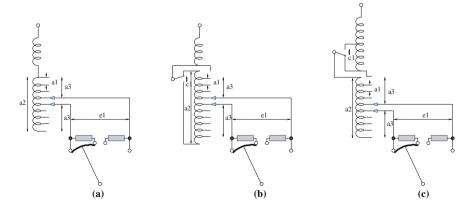

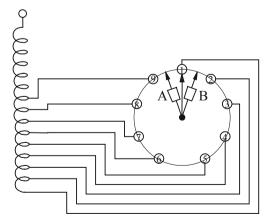

Another new configuration is shown in Fig. 1.15 [13]. In this configuration selector switches and diverter switches have not been separated. The fixed contacts have been designed such that they can pass the rated current through transformer. Diverter contacts each consists of three movable contacts. These contacts (one main contact and two auxiliary contacts) must also stand against the rated current. However, there is no need to turn the current on and off.

**Fig. 1.15** Another hybrid tap-changer

Fig. 1.16 Stages of tap-changing in hybrid tap-changer of Fig. 1.15 [13]

The movable contacts move circularly. A and B in Fig. 1.15 are solid-state switches which are similar to the configuration of Fig. 1.14, and are made up of switches which can be extinguished via the gate.

Stages of tap-changing in this configuration have been presented in Fig. 1.16 and described as follows (as an example the tap-changing process from tap 1 to tap 2 is described).

- a. The main contact is connected to tap 1 and auxiliary contacts are placed on both sides of this contact. To change the tap to tap 2, the following stages are followed.

- b. The auxiliary contacts move in CW, so that auxiliary is contacted A to contact 1 and auxiliary contact B to contact 2. In this case, solid-state switches A and B are off and no current passes the auxiliary contacts.

- c. The main contact begins to move and at the same time solid-state switch A is on.

- d. The main contact is disconnected from contact 1, but this is done with a minimum arc because solid-state switch A is on.

- e. At the instant of zero current crossing, solid-state switch A is off and B is on. Therefore, the current is transferred from the auxiliary contact of switch A to the auxiliary contact of switch B.

- f. The main contact continues its move approaching fixed contact number 3. In connecting the main contact to contact 2 no arc appears, because solid-state switch B is in the "on" position.

- g. Solid-state switch B is off and total current is transferred to the main contact.

- h. The main contacts move and are placed on both sides of contact 2. Thus the process of tap-changing from tap 1 to tap 2 ends.

Referring to the suggested circuits of the hybrid tap-changers, it can be concluded that the hybrid tap-changers can largely extinguished the arc during tap-changing, using solid-state power switches [21]. However, in these tap-changers there are still movable mechanical parts and this complicates the system and leads to the rather slow operation of the tap-changers. Meanwhile, some suggest to remove the passing resistors which decreases the tap-changing case losses.

Faster tap-changing is possible using the full-electronic version. In the next section this type of tap-changer is discussed.

### 1.5 Full-Electronic Tap-Changers

There is no movable part in full-electronic tap-changers and only solid-state power switches are used. The basic advantages of the full-electronic tap-changers are as follows:

### a. Very Low Maintenance Cost

There is no movable mechanical part in full-electronic tap-changers, and no arc can appear during the tap-changing process as there is basically no contact; therefore the maintenance cost is very low (almost zero).

### b. High Speed

The very fast switching process of solid-state power switches leads to the fast tap-changing in full-electronic tap-changers, as such that it is possible to change the tap at least once in any half-cycle.

### c. Tap Jumping

There is no passing resistor in the full-electronic tap-changers and basically the circulation current between the taps is zero, so tap jumping becomes possible.

### d. Better Performance

High speed and controllability of the solid-state switches and non-existence of mechanical limitations in the configuration of these switches enhance the capability and performance of the full-electronic tap-changers. Some of these capabilities are as follows:

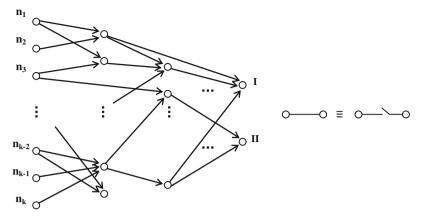

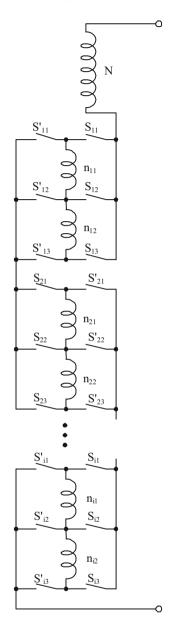

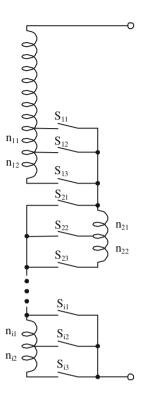

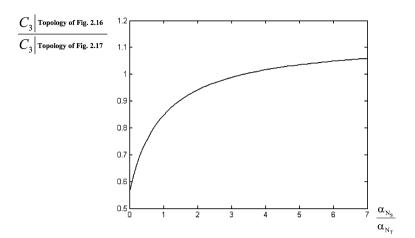

- 1. Obtaining more steps with lower tap numbers and solid-state power switches. The reason is that there is non-limit in the configuration of the solid-state power switches.

- A full-electronic tap-changer is a rapid static regulator as such that it can be considered as a custom power devices in power quality. It is capable to compensate the voltage sag, swell and also flicker.

### e. Non-limit in tap-changing time.

The reason is that if power switches are correctly switched-on there will be slight fatigue in the switches. Of course, besides of the above-mentioned advantages, full-electronic tap-changers have some problems and limitations. These limitations are as follows:

a. Switch-on voltage drop of solid-state switch is larger than that of the mechanical switch, so operational losses of the full-electronic tap-changer is higher than that of the mechanical tap-changer.

- b. Cost of full-electronic tap-changer is higher than that of the mechanical tap-changers because there are many solid-state power switch in the full-electronic tap-changer.

- c. Full-electronic tap-changers must stand against short-circuit faults and large transient peaks in power system voltage due to the lightening.

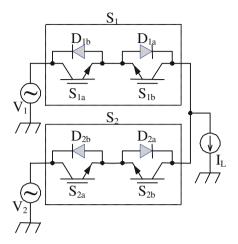

Although the idea of the full-electronic tap-changers was proposed in 1973 [22, 23], they was restricted for special applications. The first comprehensive and academic study of this system was carried out in the 90 decay [24], then research continued. To introduce the progress and research trend on full-electronic tap-changers and to clarify its position, activities in this area are reviewed.

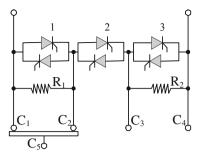

The conventional technique of using passing impedance for restricting the circulating current between the taps during tap-changing is also usable in the full-electronic tap-changers [24].

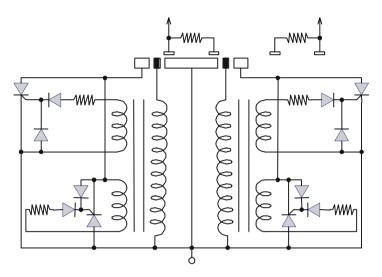

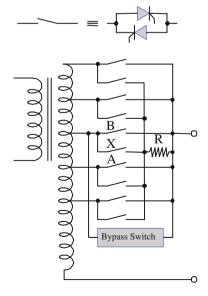

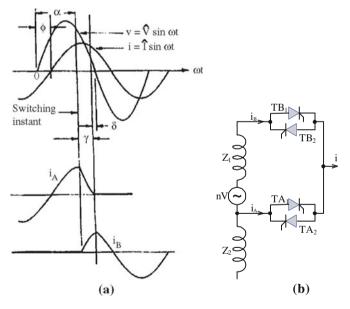

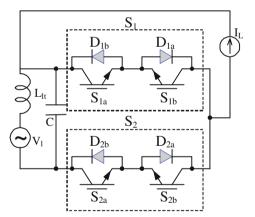

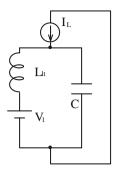

Figure 1.17 presents a typical configuration of this tap-changer. In this figure, all switches are AC solid-state power switches which are realized by pair-thyristor.

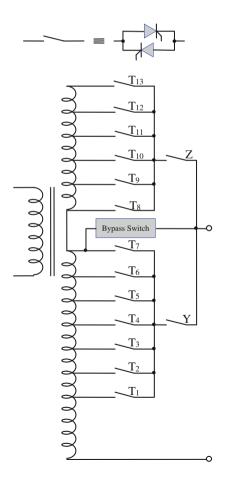

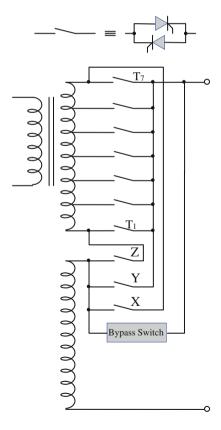

Bypass switch which may consist of a vacuum switch and/or a pair-thyristor with power higher than other thyristors, is used to bypass the fault conditions or transformer energization and protection of remaining thyristors. In tap-changer, Fig. 1.17, in order to change tap A to tap B, without taking into account the load power factor, the following stages are followed:

- a. Initially the gate command of switch A is off and at the same time the gate command of switch X is on.

- b. In the next cycle, the gate command of switch X and B are on both at the same time.

Fig. 1.17 The configuration of a typical full-electronic tap-changer using passing impedance [24]

Fig. 1.18 An electronic tap-changer with no passing impedance [24]

**Fig. 1.19** Circuit model for secondary of tapped-transformer of Fig. 1.18

It is noted that the thyristors are turned-on by the gate commands, but they are not necessarily turned-off by the gate's off command. Basically the gate's off command or inverse applied voltage causes the thyristor current to approximate to zero. Therefore, when a gate command of pair-thyristor A is off and that of pair-thyristor X held, pair-thyristor X is not necessarily turned-off while pair-thyristor X is on and ready to let the current pass. Therefore, there is probably a circulating

Fig. 1.20 Commutation of the current of switches during changing tap A to tap B in the presence of leakage impedance

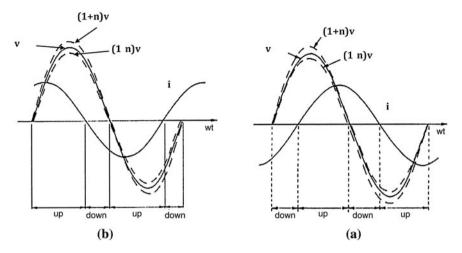

Fig. 1.21 Permissible switching time intervals for no circulating current: a inductive power factor and b capacitive power factor [24]

current between thyristors A and X limited by passing impedance R. After it can be insured that thyristor A is fully off and the second stage of tap-changing continues. It can be shown that if pair-thyristor X and B are on throughout zero-voltage crossing, there will be minimum stress on them [24]. However, a proper

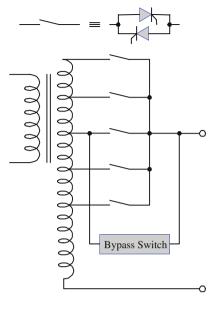

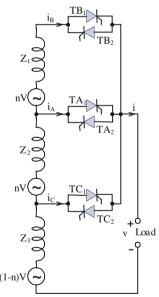

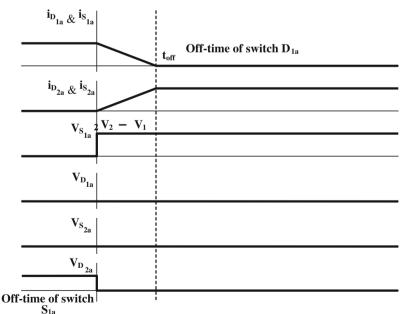

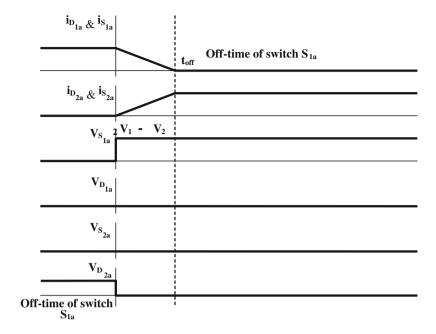

switching strategy for thyristors in configuration of Fig. 1.17 can be applied to the thyristors in Fig. 1.17 with no circulating current, where the passing impedance has been removed and the number of switches is reduced by half. Such configuration has been shown in Fig. 1.18. To evaluate the performance of this type of a tap-changer, the circuit mode of transformer is considered as Fig. 1.19. To simplify the figure, only three taps have been shown. The presented impedances are the leakage impedances of the secondary of transformer.

In Fig. 1.19, switch A (pair-thyristor  $TA_1$  and  $TA_2$ ) carries the load current, then the secondary voltage will go up or down rise by increasing or decreasing the tap (switch on of switch B) the tap (switch C is on). For tap-changing A to B or C, gate command of switch A stops and gate command of the proposed switch will be on. However, if no care is taken at this operation, there will be a probable taps short circuit for about one cycle. This short circuit current can damage the switches or the transformer winding. To prevent this short circuit, the switching instant must be precisely controlled. If the leakage impedances in model of Fig. 1.19 are

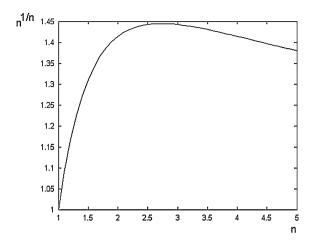

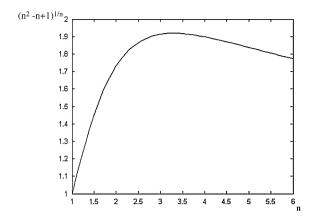

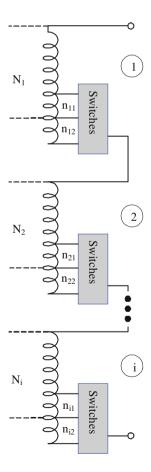

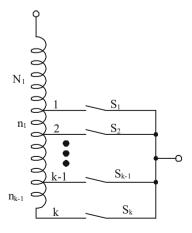

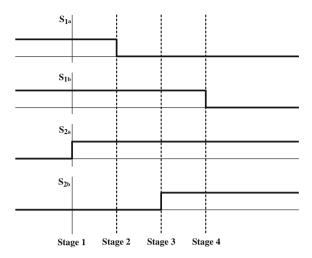

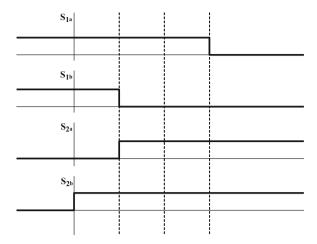

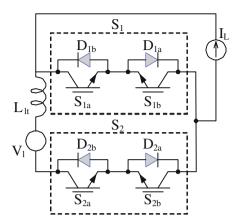

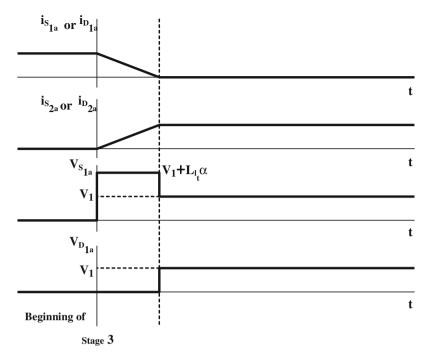

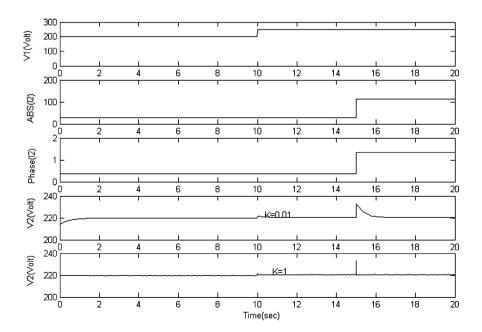

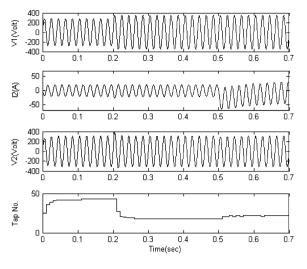

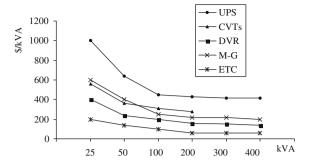

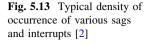

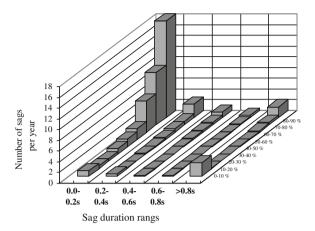

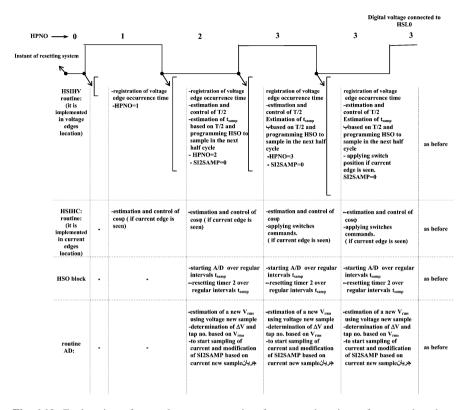

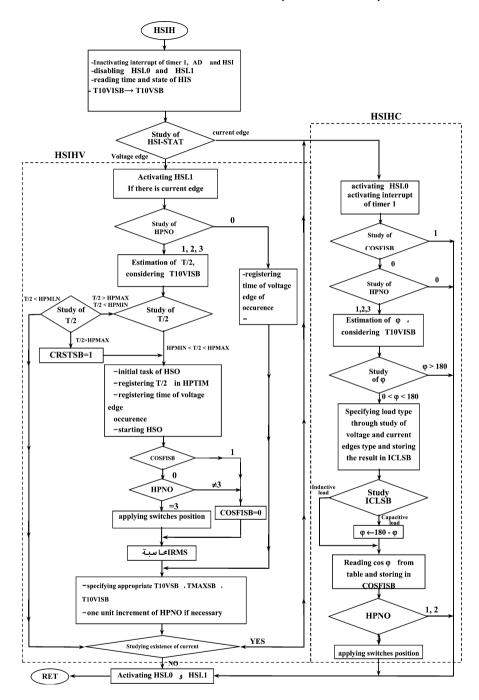

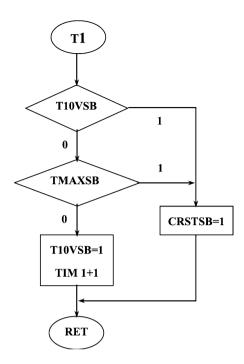

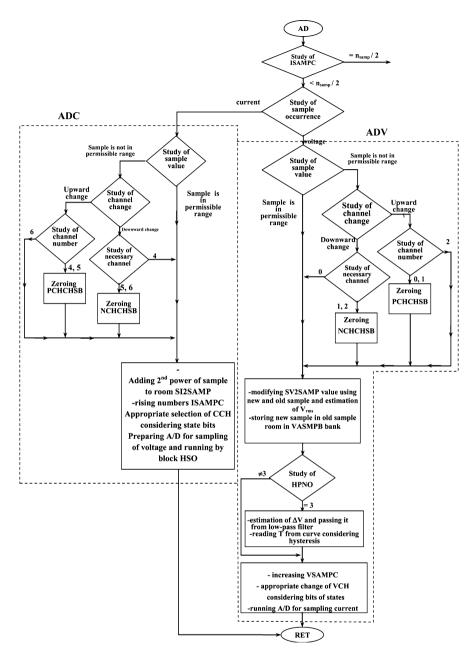

**Fig. 1.22** A full-electronic tap-changer configuration for reduction of switches voltage [24]