THIRD EDITION

Computer Hardware

## **Thomas Sterling**

California Institute of Technology and NASA Jet Propulsion Laboratory

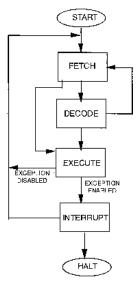

- I. Introduction

- II. A Taxonomy of Cluster Computing

- III. A Brief History of Cluster Computing

- IV. Cluster Hardware Components

- V. Cluster Software Components

- VI. Summary and Conclusions

#### **GLOSSARY**

**Cluster** A computing system comprising an ensemble of separate computers (e.g., servers, workstations) integrated by means of an interconnection network cooperating in the coordinated execution of a shared workload.

Commodity cluster A cluster consisting of computer nodes and network components that are readily available COTS (commercial off-the-shelf) systems and that contain no special-purpose components unique to the system or a given vendor product.

**Beowulf-class system** A commodity cluster implemented using mass-market PCs and COTS network technology for low-cost parallel computing.

**Constellation** A cluster for which there are fewer SMP nodes than there are processors per node.

**Message passing** A model and methodology of parallel processing that organizes a computation in separate concurrent and cooperating tasks coordinated by means of the exchange of data packets.

**CLUSTER COMPUTING** is a class of parallel computer structure that relies on cooperative ensembles of independent computers integrated by means of interconnection networks to provide a coordinated system capable of processing a single workload. Cluster computing systems achieve high performance through the simultaneous application of multiple computers within the ensemble to a given task, processing the task in a fraction of the time it would ordinarily take a single computer to perform the same work. Cluster computing represents the most rapidly growing field within the domain of parallel computing due to its property of exceptional performance/price. Unlike other parallel computer system architectures, the core computing elements, referred to as nodes, are not custom designed for high performance and parallel processing but are derived from systems developed for the industrial, commercial, or commodity market sectors and applications. Benefiting from the superior cost effectiveness of the mass production and distribution of their COTS (commercial off-the-shelf) computing nodes, cluster systems exhibit order-of-magnitude cost advantage with respect to

their custom-designed parallel computer counterparts delivering the same sustained performance for a wide range of (but not all) computing tasks.

#### I. INTRODUCTION

Cluster computing provides a number of advantages with respect to conventional custom-made parallel computers for achieving performance greater than that typical of uniprocessors. As a consequence, the emergence of clusters has greatly extended the availability of high-performance processing to a much broader community and advanced its impact through new opportunities in science, technology, industry, medical, commercial, finance, defense, and education among other sectors of computational application. Included among the most significant advantages exhibited by cluster computing are the following:

- Performance scalability. Clustering of computer nodes provides the means of assembling larger systems than is practical for custom parallel systems, as these themselves can become nodes of clusters. Many of the entries on the Top 500 list of the world's most powerful computers are clusters and the most powerful general-purpose computer under construction in the United States (DOE ASCI) is a cluster to be completed in 2003.

- *Performance to cost.* Clustering of mass-produced computer systems yields the cost advantage of a market much wider than that limited to the high-performance computing community. An order of magnitude priceperformance advantage with respect to custom-designed parallel computers is achieved for many applications.

- Flexibility of configuration. The organization of cluster systems is determined by the topology of their interconnection networks, which can be determined at time of installation and easily modified. Depending on the requirements of the user applications, various system configurations can be implemented to optimize for data flow bandwidth and latency.

- Ease of upgrade. Old components may be replaced or new elements added to an original cluster to incrementally improve system operation while retaining much of the initial investment in hardware and software.

- Architecture convergence. Cluster computing offers a single general strategy to the implementation and application of parallel high-performance systems independent of specific hardware vendors and their product decisions. Users of clusters can build software application systems with confidence that such systems will be available to support them in the long term.

- *Technology tracking*. Clusters provide the most rapid path to integrating the latest technology for high-

performance computing, because advances in device technology are usually first incorporated in mass market computers suitable for clustering.

• *High availability*. Clusters provide multiple redundant identical resources that, if managed correctly, can provide continued system operation through graceful degradation even as individual components fail.

Cluster computing systems are comprised of a hierarchy of hardware and software component subsystems. Cluster hardware is the ensemble of compute nodes responsible for performing the workload processing and the communications network interconnecting the nodes. The support software includes programming tools and system resource management tools. Clusters can be employed in a number of ways. The master-slave methodology employs a number of slaved compute nodes to perform separate tasks or transactions as directed by one or more master nodes. Many workloads in the commercial sector are of this form. But each task is essentially independent, and while the cluster does achieve enhanced throughput over a single processor system, there is no coordination among slave nodes, except perhaps in their access of shared secondary storage subsystems. The more interesting aspect of cluster computing is in support of coordinated and interacting tasks, a form of parallel computing, where a single job is partitioned into a number of concurrent tasks that must cooperate among themselves. It is this form of cluster computing and the necessary hardware and software systems that support it that are discussed in the remainder of this article.

# II. A TAXONOMY OF CLUSTER COMPUTING

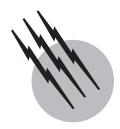

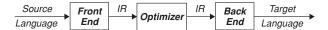

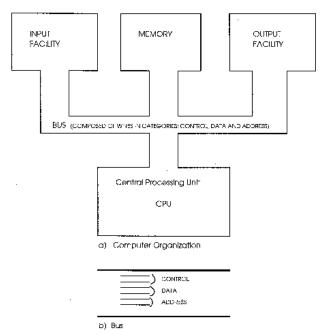

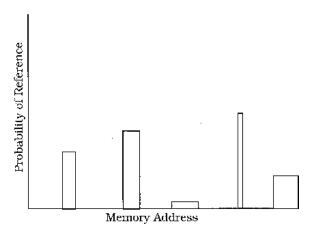

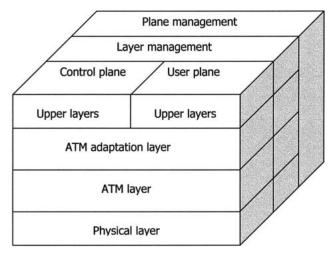

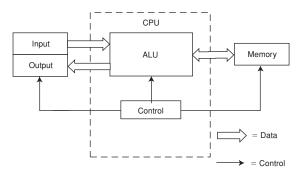

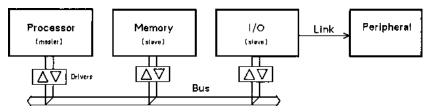

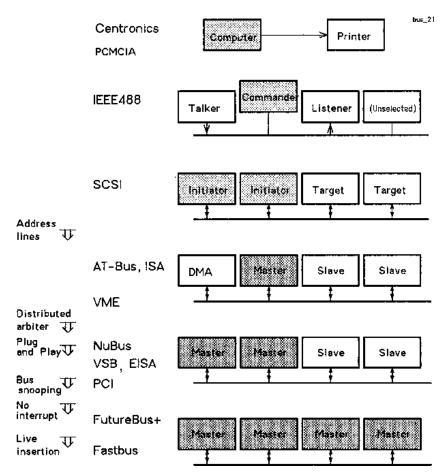

Cluster computing is an important class of the broader domain of parallel computer architecture that employs a combination of technology capability and subsystem replication to achieve high performance. Parallel computer architectures partition the total work to be performed into many smaller coordinated and cooperating tasks and distribute these tasks among the available replicated processing resources. The order in which the tasks are performed and the degree of concurrency among them are determined in part by their interrelationships, precedence constraints, type and granularity of parallelism exploited, and number of computing resources applied to the combined tasks to be conducted in concert. A major division of parallel computer architecture classes, which includes cluster computing, includes the following primary (but not exhaustive) types listed in order of their level of internal communication coupling measured in terms of bandwidth

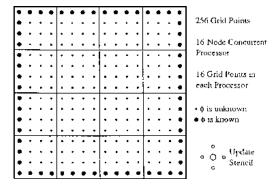

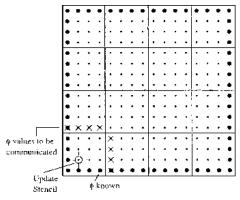

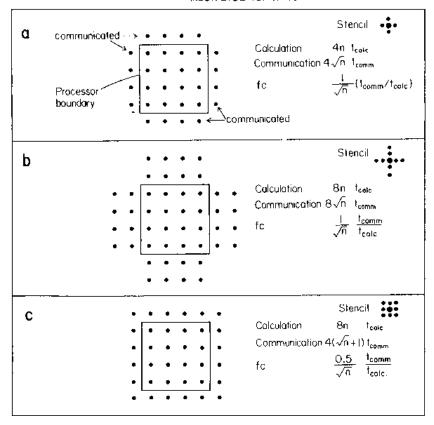

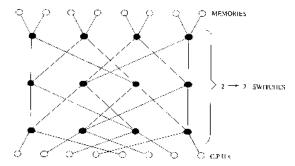

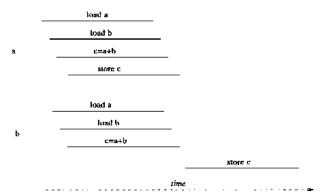

(communication throughput) and latency (delay in transfer of data). This taxonomy is illustrated in Figure 1. Such a delineation is, by necessity, somewhat idealized because many actual parallel computers may incorporate multiple forms of parallel structure in their specific architecture. Also, the terminology below reflects current general usage but the specific terms below have varied in their definition over time (e.g., "MPP" originally was applied to fine-grain SIMD computers, but now is used to describe large MIMD computers).

- 1. Vector processing. The basis of the classical supercomputer (e.g., Cray 1), this fine-grain architecture pipelines memory accesses and numeric operations through one or more multistage arithmetic units supervised by a single controller.

- 2. *Systolic*. Usually employed for special-purpose computing (e.g., digital signal and image processing), systolic systems employ a structure of logic units and physical communication channels that reflect the computational organization of the application algorithm control and data flow paths.

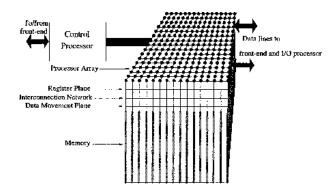

- 3. SIMD. This Single instruction stream, multiple data stream or SIMD family employs many fine- to medium-grain arithmetic/logic units (more than tens of thousands), each associated with a given memory block (e.g., Maspar-2, TMC CM-5). Under the management of a single system-wide controller, all units perform the same operation on their independent data each cycle.

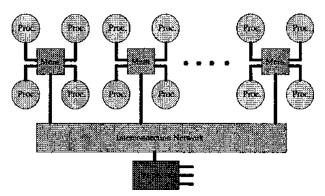

- 4. MPP. This multiple instruction stream, multiple data stream or MIMD class of parallel computer integrates many (from a few to several thousand) CPUs (central processing units) with independent instruction streams and flow control coordinating through a high-bandwidth, low-latency internal communication network. Memory blocks associated with each CPU may be independent of the oth-

- ers (e.g., Intel Paragon, TMC CM-5), shared among all CPUs without cache coherency (e.g., CRI T3E), shared in SMPs (symmetric multiprocessors) with uniform access times and cache coherence (e.g., SGI Oracle), or shared in DSMs (distributed shared memory) with nonuniform memory access times (e.g., HP Exemplar, SGI Origin).

- 5. Cluster computing. Integrates stand-alone computers devised for mainstream processing tasks through local-area (LAN) or system-area (SAN) interconnection networks and employed as a singly administered computing resource (e.g., Beowulf, NOW, Compaq SC, IBM SP-2).

- 6. Distributed Internet computing. Employs wide-area networks (WANs) including the Internet to coordinate multiple separate computing systems (possibly thousands of kilometers apart) under independent administrative control in the execution of a single parallel task or workload. Previously known as metacomputing and including the family of GRID management methods, this emergent strategy harnesses existing installed computing resources to achieve very high performance and, when exploiting otherwise unused cycles, superior price/performance.

Cluster computing may be distinguished among a number of subclasses that are differentiated in terms of the source of their computing nodes, interconnection networks, and dominant level of parallelism. A partial classification of the domain of cluster computing includes commodity clusters (including Beowulf-class systems), proprietary clusters, open clusters or workstation farms, super clusters, and constellations. This terminology is emergent, subjective, open to debate, and in rapid transition. Nonetheless, it is representative of current usage and practice in the cluster community.

A definition of commodity clusters developed by consensus is borrowed from the recent literature and reflects their important attribute; that they comprise components

FIGURE 1 Taxonomy of cluster computing.

that are entirely off-the-shelf, i.e., already developed and available for mainstream computing:

A commodity cluster is a local computing system comprising a set of independent computers and a network interconnecting them. A cluster is local in that all of its component subsystems are supervised within a single administrative domain, usually residing in a single room and managed as a single computer system. The constituent computer nodes are commercial-off-theshelf, are capable of full independent operation as is, and are of a type ordinarily employed individually for stand-alone mainstream workloads and applications. The nodes may incorporate a single microprocessor or multiple microprocessors in a symmetric multiprocessor (SMP) configuration. The interconnection network employs COTS LAN or SAN technology that may be a hierarchy of or multiple separate network structures. A cluster network is dedicated to the integration of the cluster compute nodes and is separate from the cluster's external (worldly) environment. A cluster may be employed in many modes including but not limited to high capability or sustained performance on a single problem, high capacity or throughput on a job or process workload, high availability through redundancy of nodes, or high bandwidth through multiplicity of disks and disk access or I/O channels.

Beowulf-class systems are commodity clusters employing personal computers (PCs) or small SMPs of PCs as their nodes and using COTS LANs or SANs to provide node interconnection. A Beowulf-class cluster is hosted by an open source Unix-like operating system such as Linux. A Windows-Beowulf system runs the mass-market widely distributed Microsoft Windows operating systems instead of Unix.

Proprietary clusters incorporate one or more components that are custom-designed to give superior system characteristics for product differentiation through employing COTS components for the rest of the cluster system. Most frequently proprietary clusters have incorporated custom-designed networks for tighter system coupling (e.g., IBM SP-2). These networks may not be procured separately (unbundled) by customers or by OEMs for inclusion in clusters comprising other than the specific manufacturer's products.

Workstation farms or open clusters are collections of previously installed personal computing stations and group shared servers, loosely coupled by means of one or more LANs for access to common resources, that, although primarily employed for separate and independent operation, are occasionally used in concert to process single coordinated distributed tasks. Workstation farms provide superior performance/price over even other cluster types in that they exploit previously paid-for but otherwise unused computing cycles. Because their interconnection network is shared for other purposes and not op-

timized for parallel computation, these open clusters are best employed for weakly interacting distributed workloads. Software tools such as Condor facilitate their use while incurring minimum intrusion to normal service.

Super clusters are clusters of clusters. Principally found within academic, laboratory, or industrial organizations that employ multiple clusters for different departments or groups, super clusters are established by means of WANs integrating the disparate clusters into a single more loosely coupled computing confederation.

Constellations reflect a different balance of parallelism than conventional commodity clusters. Instead of the primary source of parallelism being derived from the number of nodes in the cluster, it is a product of the number of processors in each SMP node. To be precise, a constellation is a cluster in which there are more processors per SMP node than there are nodes in the cluster. While the nodes of a constellation must be COTS, its global interconnection network can be of a custom design.

Of these, commodity clusters have emerged as the most prevalent and rapidly growing segment of cluster computing systems and are the primary focus of this article.

# III. A BRIEF HISTORY OF CLUSTER COMPUTING

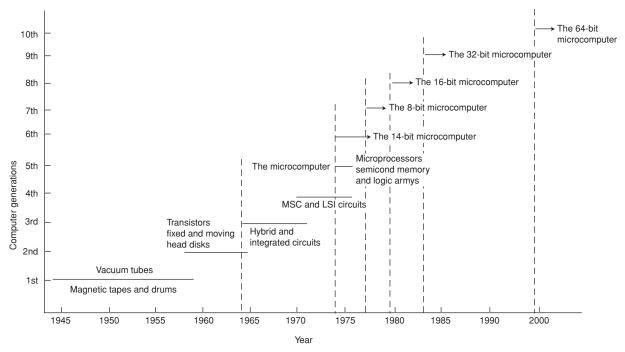

Cluster computing originated within a few years of the inauguration of the modern electronic stored-program digital computer. SAGE was a cluster system built for NORAD under an Air Force contract by IBM in the 1950s based on the MIT Whirlwind computer architecture. Using vacuum tube and core memory technologies, SAGE consisted of a number of separate stand-alone systems cooperating to manage early warning detection of hostile airborne intrusion of the North American continent. Early commercial applications of clusters employed paired loosely coupled computers with one performing user jobs while the other managed various input/output devices.

Breakthroughs in enabling technologies occurred in the late 1970s, both in hardware and software, that were to have a significant long-term effect on future cluster computing. The first generations of microprocessors were designed with the initial development of VLSI technology and by the end of the decade the first workstations and personal computers were being marketed. The advent of Ethernet provided the first widely used LAN technology, creating an industry standard for a modest cost multidrop interconnection medium and data transport layer. Also at this time, the multitasking Unix operating system was created at AT&T Bell Labs and extended with virtual memory and network interfaces at UC Berkeley. Unix was adopted in its various commercial and public domain forms by the

scientific and technical computing community as the principal environment for a wide range of computing system classes from scientific workstations to supercomputers.

During the decade of the 1980s, increased interest in the potential of cluster computing was marked by important experiments in research and industry. A collection of 160 interconnected Apollo workstations was employed as a cluster to perform certain computational tasks by the NSA. Digital Equipment Corporation developed a system comprising interconnected VAX 11/750s, coining the term cluster in the process. In the area of software, task management tools for employing workstation farms were developed, most notably the Condor software package from the University of Wisconsin. The computer science research community explored different strategies for parallel processing during this period. From this early work came the communicating sequential processes model more commonly referred to as the message-passing model, which has come to dominate much of cluster computing today.

An important milestone in the practical application of the message passing model was the development of PVM (parallel virtual machine), a library of linkable functions that could allow routines running on separate but networked computers to exchange data and coordinate their operation. PVM, developed by Oak Ridge National Laboratory, Emory University, and University of Tennessee, was the first major open distributed software system to be employed across different platforms. By the beginning of the 1990s, a number of sites were experimenting with clusters of workstations. At the NASA Lewis Research Center, a small cluster of IBM workstations was used to simulate the steady-state behavior of jet aircraft engines in 1992. The NOW (Network of Workstations) project at UC Berkeley began operation of the first of several clusters there in 1993 that led to the first cluster to be entered on the Top 500 list of the world's most powerful computers. Also in 1993, one of the first commercial SANs, Myrinet, was introduced for commodity clusters, delivering improvements in bandwidth and latency an order of magnitude better than the Fast Ethernet LAN most widely used for the purpose at that time.

The first Beowulf-class PC cluster was developed at NASA's Goddard Space Flight Center in 1994 using early releases of the Linux operating system and PVM running on 16 Intel 100-MHz 80486-based PCs connected by dual 10-Mbps Ethernet LANs. The Beowulf project developed the necessary Ethernet driver software for Linux and additional low-level cluster management tools and demonstrated the performance and cost effectiveness of Beowulf systems for real-world scientific applications. That year, based on experience with many other message-passing software systems, the parallel computing community set

out to provide a uniform set of message-passing semantics and syntax and adopted the first MPI standard. MPI has become the dominant parallel computing programming standard and is supported by virtually all MPP and cluster system vendors. Workstation clusters running the Sun Microsystems Solaris operating system and NCSA's PC cluster running the Microsoft NT operating system were being used for real-world applications.

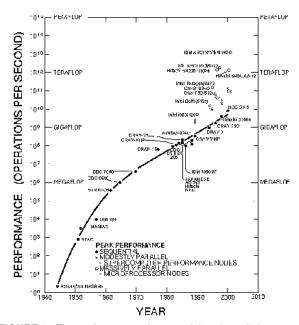

In 1996, the Los Alamos National Laboratory and the California Institute of Technology with the NASA Jet Propulsion Laboratory independently demonstrated sustained performance of more than 1-Gflops for Beowulf systems costing under \$50,000 and was awarded the Gordon Bell Prize for price/performance for this accomplishment. By 1997 Beowulf-class systems of more than 100 nodes had demonstrated sustained performance of greater than 10 Gflops with a Los Alamos system making the Top 500 list. By the end of the decade, 28 clusters were on the Top 500 list with a best performance of more than 500 Gflops. In 2000, both DOE and NSF announced awards to Compaq to implement their largest computing facilities, both clusters of 30 and 6 Tflops, respectively.

#### IV. CLUSTER HARDWARE COMPONENTS

Cluster computing in general and commodity clusters in particular are made possible by the existence of costeffective hardware components developed for mainstream computing markets. The capability of a cluster is determined to first order by the performance and storage capacity of its processing nodes and the bandwidth and latency of its interconnection network. Both cluster node and cluster network technologies evolved during the 1990s and now exhibit gains of more than two orders of magnitude in performance, memory capacity, disk storage, and network bandwidth and a reduction of better than a factor of 10 in network latency. During the same period, the performance-to-cost ratio of node technology has improved by approximately 1000. In this section, the basic elements of the cluster node hardware and the alternatives available for interconnection networks are briefly described.

#### A. Cluster Node Hardware

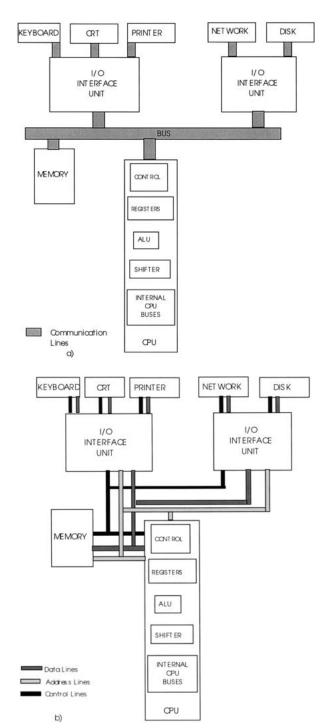

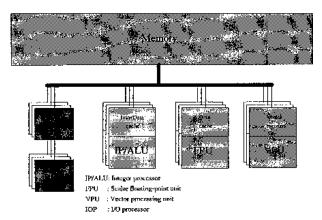

The processing node of a cluster incorporates all of the facilities and functionality necessary to perform a complete computation. Nodes are most often structured either as uniprocessor systems or as SMPs although some clusters, especially constellations, have incorporated nodes that were distributed shared memory (DSM) systems. Nodes are distinguished by the architecture of

the microprocessors employed, the number and organization of the microprocessors, the capacities of the primary and secondary storage, and the internal interconnect logic structure. The nodes of commodity clusters marketed primarily for mainstream computing environments must also incorporate standard interfaces to external devices that ensure interoperability with myriad components developed by third-party vendors. The use of the high-bandwidth interface allows clusters to be configured with little or no change to the node subsystem, minimizing any additional costs incurred on a per-node basis. The key elements of a node are briefly discussed below. It must be understood that this technology is evolving rapidly and that the specific devices that are provided as examples are likely to be upgraded in operational characteristics or to be replaced altogether in the near future.

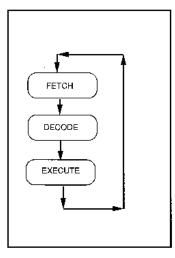

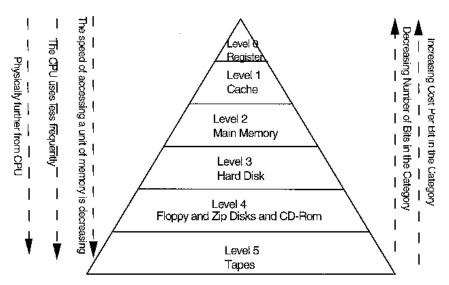

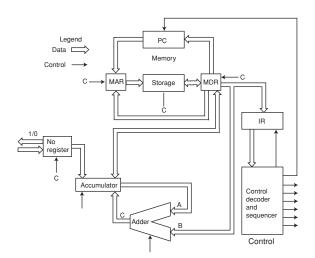

- 1. Central processing unit. The CPU is a single VLSI integrated circuit microprocessor, possibly merged on an MCM (multichip module) with one or more cache chips. The CPU executes sequences of binary instructions operating on binary data, usually of 32- or 64-bit length. While many instructions are performed on internal data stored in registers, acquiring new data from the memory system is an important aspect of microprocessor operation, requiring one or more high-speed cache memories to minimize the average load/store access times. Both 32-bit and 64-bit architectures are used in clusters with the most popular based on the 32-bit Intel X86 family and the highest performance clusters based on the 64-bit Compaq Alpha family or IBM RS6000. The first Beowulf-class commodity clusters incorporated Intel 80486 microprocessors operating at 100 MHz. Today, descendents of this chip including the Intel Pentium III and the AMD K7 Athelon have clock rates in excess of 1 GHz. The CPU connects to an internal memory bus for high-speed data transfers between memory and CPU and to an external I/O bus that provides interfaces to secondary storage and networking control modules.

- 2. Main memory. Stores the working data and program instructions to be processed by the CPU. It is a part of a larger memory hierarchy that includes high-speed cache memories closer to the CPU and high-density persistent mass storage from which it acquires its initial data and stores its final results. For the last two decades, main memory has been dominated by DRAM technology, closely packed arrays of switched capacitive cells embedded on silicon wafers. DRAM chips containing 256 Mbits of data are available with gigabit chips to become common place in the near future. Typical cluster nodes support main memory capacities between 64 Mbytes and 1 Gbytes although large SMP or DSM nodes provide more. DRAM has undergone significant advances in recent years pro-

viding more rapid throughput as well as higher density, reducing if not closing the bottleneck between CPU and its main memory.

- 3. Secondary storage. Comprises a set of devices that provides persistent storage of a large amount of data. Secondary storage serves several purposes as a function of the usage of the data it contains. It provides all of the functions, both user applications and operating system tools, that govern the operation and computation of the CPU. It provides the data sets on which the user tasks are to operate and is the primary repository for the final results of user computations. It maintains configuration data concerning the setup and operational parameters of the computing node as well as information concerning the rest of the cluster devices and their relational roles. Because most memory systems support the virtual memory abstraction, providing a logical memory many times larger than the actual physical main memory installed, secondary storage temporarily holds those segments of the logical address space and associated data that do not fit in the existing physical main memory. Unlike main memory, data stored on secondary storage devices are retained, even when system power is disrupted. This nonvolatile property allows data to be archived indefinitely. The primary component type providing secondary storage is the venerable hard disk with its early genesis in the late 1950s based on magnetic storage (like a cassette tape) of one or more disks rotating on a single spindle at high speed and accessed by a magnetic detection head moved radically in and out across the disk surface, reminiscent of the arm of an old record turntable. Modern disk drives provide many tens of gigabytes at moderate cost and access times on the order of a few milliseconds. Other technologies are employed to provide more specialized forms of secondary storage, particularly for data portability and safe permanent archival storage. CD-ROMs developed from the original digital musical recording media provide approximately 600 Mbytes of storage at less than \$1 a disk and read-write capability is now becoming commonplace, although this is of less importance to cluster systems. The long-lived and relatively diminutive floppy disk holding a mere 1.4 Mbytes is still employed, even on clusters, primarily for initial installation, configuration, and boot up.

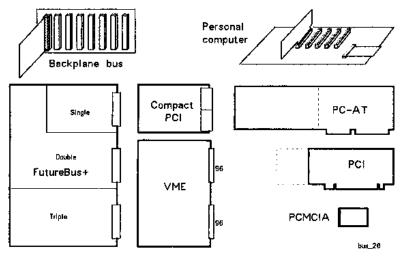

- 4. External interfaces. Serve three important roles related to the operation and management of clusters. They provide direct user interactive access and control, they permit application data input and results to be conveyed with devices outside the system, and they connect to the cluster interconnection network and thereby to other nodes in the cluster. While there are many different types of interfaces (just look at the number of sockets on the back of a typical PC), PCI is universal from PCs to mainframes, connecting

the CPU to a plethora of interface control devices. The PCI bus has four different configurations employing 32-or 64-bit connections running at 33- or 66-MHz clock speed and a peak data throughput of 4 Gbps. The majority of network interface controllers (NIC) are compatible with one or more of these PCI forms. In the future, it is likely that a new external interface standard, Infiniband, will eventually replace PCI to deliver higher throughput and lower latency between the CPU and external devices.

#### **B. Cluster Network Hardware**

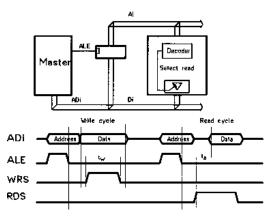

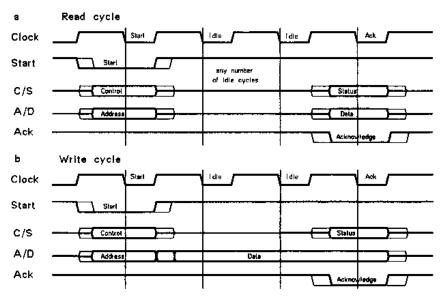

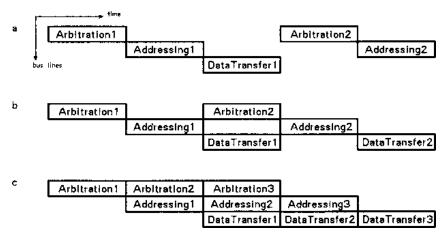

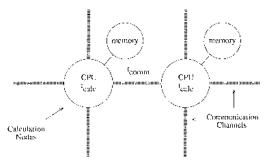

A model, but not necessarily the only possible model, of parallel processing with cluster systems involves each of the cluster nodes performing one or more tasks on local data and then exchanging the computed results with other nodes within the cluster. Networks make this possible. They provide physical channels between nodes by which data are transported and logical protocols that govern the flow and interpretation of the transferred data. Networks are employed in a broad range of integrated systems from the Internet spanning the globe requiring possibly as much as a hundred milliseconds for a message packet to reach its destination to a data bus internal to a computer integrating its various components supporting data transfers in 100 nanosec or less, a ratio of a million in network latency. Networks for commodity clusters fall in between with the initial use of Ethernet exhibiting on average approximately 100 nanosec latency falling in the middle (logarithmically speaking).

Network technology determines the potential value of cluster computing. Its principal properties are bandwidth, latency, scale, and cost. Bandwidth imposes an upper bound on the amount of data that can be transferred in unit time (e.g., Mbps, Gbps). Latency is the amount of time it takes for a message packet to transit the diameter of a system measured in microseconds. Cost is usually considered as the percentage of the total price of the hardware system. Scale is the largest number of nodes that a network can connect effectively. Together, they establish a cluster's capability, applicability, and user accessibility. Different applications exhibit varying global data access patterns that may be suitable for some networks rather than others. Higher bandwidth networks ordinarily will have greater generality of application than those networks of lower bandwidth. Similarly, for applications using short messages or involving frequent global synchronization, lower latency networks will be more general purpose than high-latency networks. But superior behavioral properties often come at additional cost that may preclude their use in many environments, where cost is a significant factor in the choice to employ clusters in the first place. Thus the selection of a specific network is dependent on how the cluster is to be used and by whom.

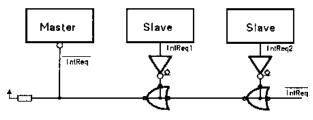

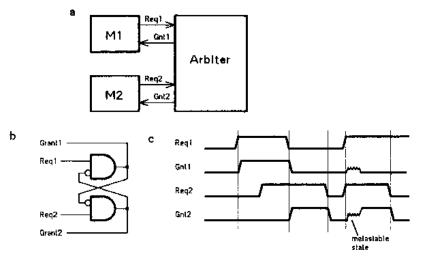

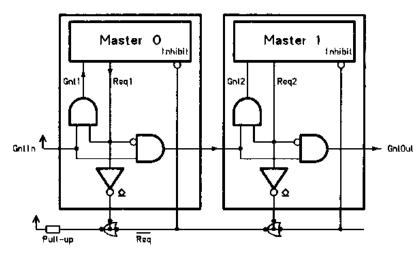

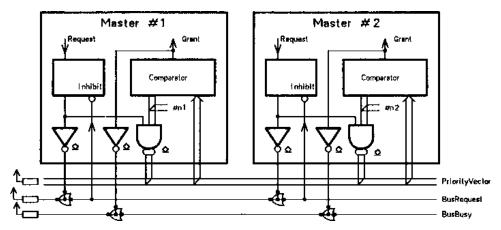

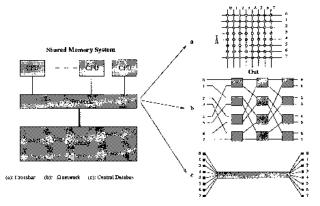

A cluster network includes NICs that connect the cluster node to the network, transport layer links to carry the data, and switches that route the data through the network. NICs move data from message buffers filled by the node processor to signal packets sent out to the transport layer performing a number of translation functions on the data in the process. The data links may comprise one or more parallel channels and may be implemented with metal coaxial cable or optical fiber (advanced development of free-space optical networks is under way). Switches accept messages at their multiple input ports, determine their required routing, switch as many as possible simultaneously sending them out the appropriate output ports, and arbitrating where contention for shared resources (ports, channels) occurs. The earliest Beowulf-class systems used low-cost hubs, rather than the more expensive switches, but these permitted only one transfer to occur at a time on the entire network. Switches deliver much closer to the peak bi-section bandwidth of the network as they isolate separate disjoint paths from each other.

Together these network components can be structured to form a number of different topologies. Most simple among these and used frequently for small clusters is the star configuration using a single switch of degree n (the number of separate ports) connecting n nodes. Larger systems can be formed with a hierarchy of switches to form a tree structure. The scale of tree-based clusters is limited by the bi-section bandwidth of the root node of the tree topology. More complex network structures permit the implementation of larger systems. Among them is the CLOS network (also referred to as the fat-tree) that overcomes the deficiency of the tree topology by providing multiple channels in parallel, balanced to keep the crosssection bandwidth equal at each level in the tree. Mesh and toroidal topologies provide scalable bandwidth and locality of interconnect with fixed degree nodes but may experience relatively high latency across the system diameter. Variations on these and other network topologies are possible and depend on requirements of a given system. A few of the most widely used network technologies used in commodity clusters are described next.

1. Ethernet is the most widely used network for clusters, even today, although devised as a LAN and originated in the late 1970s. Its success is due in part to its repeated reinvention, which takes advantage of technology advances while meeting expanding requirements. The 10-Mbps Ethernet that was first used in Beowulf clusters in the early 1990s superceded early Ethernet at 3 Mbps. Fast Ethernet provided 100 Mbps and with low-cost switches is the mainstay of small low-cost Beowulf-class systems.

Gigabit Ethernet, as the name implies, provides a peak bandwidth of approximately 1 Gbps. But its per-node cost remains high and it suffers from the relatively long latencies of its predecessors.

- 2. Myrinet was one of the first networks to be developed expressly for the SAN and cluster market. With a cost of approximately \$1600 per node, Myrinet was initially reserved for the more expensive workstation clusters. But with its superior latency properties of 20  $\mu$ sec or less, it permitted some classes of more tightly coupled applications to run efficiently that would perform poorly on Ethernet-based clusters. More recently, reduced pricing has expanded its suitability to lower cost systems and has proven very popular.

- 3. VIA is a recent advance in cluster network technology involving improvements in both hardware and software to further reduce data communication latency. Typically, message packets are copied from the user application space into the operating system space or vice versa. VIA (virtual interface architecture) employs a zero-copy protocol, avoiding the O/S intermediate stage and moving the packets directly between the network transport layer and the application. Giganet's cLAN and Compaq's Server net II both implement the VIA standard, delivering best case latencies well below  $10~\mu sec$ .

- 4. SCI was perhaps the first SAN to achieve IEEE standardization and has very good bandwidth and latency characteristics. Existing implementations provide between 3.2- and 8-Gbps peak bandwidth with best latencies below 4  $\mu$ sec. The SCI standard includes protocol for support of distributed shared memory operation. However, most clusters employing SCI use PCI-compatible network control cards (e.g., Dolphin) that cannot support cross-node cache coherence. Nonetheless, even in distributed memory clusters, it provides an effective network infrastructure.

- 5. Infiniband is the next-generation interconnection technology to extend the capabilities of SANs. Although not yet available, an industrial consortium of major computer technology (hardware and software) manufacturers has developed and released an extensive specification that will lead first to reference implementations, and eventually to widely distributed products. Bandwidths up to 12 Gbps (employing optical channels) and latencies approaching 1  $\mu$ sec will become possible with Infiniband, which replaces previous I/O buses (e.g., PCI) and migrates the network interconnect closer to the memory bus of the compute node.

#### V. CLUSTER SOFTWARE COMPONENTS

The earliest use of commodity clusters involved little more software than the original node operating system and basic support for a network interface protocol such as sockets in Unix. Application programmers running a single problem on a small, dedicated cluster would hand craft the parallel program and painstakingly install the code and necessary data individually on every node of the cluster system. Good results were obtained for real-world problems on Beowulf-class systems and other such clusters, motivating continued advances in cluster hardware and methodology. Today, with commodity clusters contending for dominance of the high-performance computer arena, such primitive frontier techniques can no longer be justified and, indeed, would present a serious obstacle to wider usage of commodity clusters. During the intervening period, significant advances in software support tools have been developed for cluster computing. These are in the two critical areas of programming environments and resource management tools. Together, they provide the foundation for the development of sophisticated and robust cluster system environments for industrial, commercial, and scientific application.

The environments and tools described below engage the system as a global ensemble, treating its processing nodes as a set of compute and storage resources to be managed, allocated, and programmed. But each node is itself a complete and self-sustaining logical as well as physical entity, hosting its own environment: the node operating system. While some experimental clusters incorporate custom operating systems derived expressly for use within the cluster context, the vast majority of commodity clusters employ nodes hosting conventional operating systems. Many operating systems have been used in support of clusters. The IBM AIX operating system used on their SP-2 and Compaq True64 used on their Alpha-based SC series are two examples of vendor software migrated to use with clusters. However, the dominant operating systems employed with commodity clusters are Linux and Microsoft Windows. Linux emerged as the software of choice as a result of the Beowulf Project, which implemented the first clusters using Linux and running real-world science and technical applications. Linux gained prominence because of its Unix-like structure, which was consistent with the technical computing community's environments from scientific workstations to supercomputers and because of its free open source code policy. Microsoft Windows, the world's single most widely used operating system, has been favored in business and commerce environments for clusters using ISV applications software developed for Windows such as distributed transaction processing. Windows has also been used effectively for technical computing clusters at NSCA and Cornell Theory Center. Both IBM and Compag as an alternative cluster node operating system to their proprietary software have adopted Linux.

## A. Programming Environments

Parallel programming of clusters involves a sequence of steps that transforms a set of application requirements into a set of cooperating concurrent processes and data sets. Although actual programming styles may vary significantly among practitioners, a representative methodology may be the following process:

- 1. Capture the application in a set of ordered routines.

- 2. Partition the global data into separate approximately equal regions.

- 3. Define tasks to be performed on each data partition.

- 4. Determine precedence constraints between tasks of different regions.

- In the programming language of choice, write the sequence of statements that encodes the tasks to be performed.

- 6. In the global communication medium of choice, set up synchronization conditions that will govern guarded program execution.

- 7. Devise procedures for exchanging necessary intermediate results among concurrent tasks.

- 8. Create a minimalist test data set and debug compile and runtime program errors.

- 9. Monitor program behavior and optimize code for best performance.

- 10. Partition real-world data set.

- 11. On selected cluster, allocate nodes to data partitions.

- 12. Install data and tasks on designated nodes.

- 13. Initiate execution and acquire result values.

These steps are rarely performed in such rigid lock-step manner but all of the actions described must be accomplished prior to successful completion of executing a real parallel problem on a cluster. The effectiveness achieved in programming a cluster is difficult to measure (although some metrics have been devised to this end). Nonetheless, the ease of parallel programming is strongly influenced by the execution model assumed and the tools available to assist in the process.

Many models have been conceived in the last two decades (or more) to provide a conceptual framework for parallel program execution and programming. These have been strongly influenced by the assumptions of the characteristics of the underlying parallel computer. Pipelined supercomputers used vector models, SIMD machines used fine-grain data parallel programming, SMP systems used coarse-grain multiple threads with shared memory synchronization (e.g., open MP), and large MPPs used single-program, multiple data stream (SPMD) style (e.g., HPF) with either put/get shared memory primitives or message passing for interprocessor cooperation. Because of

the relatively long global latencies and constrained network bandwidth characteristic of clusters, the programming paradigms of widest usage have been the masterslave model for embarrassingly parallel job streams of independent tasks (e.g., transaction processing, web search engines) and the message-passing model for cooperating interrelated processes. Where clusters consist of SMP nodes, hybrid models are sometimes used employing message passing between nodes and multiple threads within the nodes.

Efficient programming practices demand effective programming environments that incorporate a set of sophisticated tools to support the steps listed above. A partial list of the desired tools based on a message-passing approach might include these:

- A core language and compiler (e.g., C, Fortran)

- A language sensitive editor (e.g., Emacs)

- A linkable message-passing library [e.g., MPICH (http://www-unix.mcs.anl.gov/mpi/mpich), LAM (http://www.mpi.nd.edu/lam)]

- Numeric libraries [e.g., Scalapack (http://www.netlib. org/scalapack)]

- Debuggers [e.g., gdb, Totalview (http://www.etnus. com)]

- Performance profilers [e.g., jumpshot (http://www-unix.mcs.anl.gov/mpi/mpich), XPVM (http://epm.ornl.gov/pvm)]

- Loaders and process distribution [e.g., Scyld (http://www.scyld.com), Rocks (http://slic01.sdsc.edu),

vasystemimager (systemimager.org), OSCAR (http://openclustergroup.org), etc.]

- Schedulers [e.g., LSF (http://www.platform.com), PBS (http://www.openpbs.org), Condor (http://www.cs.wisc.edu/condor), etc.]

Such environments and tools are in a state of flux with a combination of free open-source and commercial offerings in continuous development yielding constant improvements in functionality, performance, and reliability. But new tools that provide more complete support, especially for parallel debugging, are still required. One important trend is toward the development of PSEs or problem-solving environments that target specific application domains and provide the programmer with a high-level framework within which to cast the problem. Other programming styles for clusters such as HPF, BSP, Split-C, and UPC are also being pursued and applied by some communities, although it is unclear which if any of these will become dominant.

One challenge that complicates programming clusters is the use of nodes comprising more than one processor in an SMP configuration. Such nodes view their local

memory as common, sharing the name space within the node through hardware support of cache coherence. In principle, this allows computing within each node to employ a threaded shared memory model rather than the message-passing model. One would expect that such mixed-mode programming could yield superior performance. Surprisingly, this is not the mainstream practice. The majority of users of clusters of SMP nodes program intranode operation with message-passing operations such as those provided by MPI as they do internode processing. One widely used SMP programming methodology is Open MP, which provides the added constructs necessary for parallel programming on a shared memory multiprocessor. Some programmers, striving to take advantage of both clusters and their SMP nodes, employ a hybrid programming methodology consisting of both MPI and Open MP. This has not become common practice but is expected to grow in usage, in spite of its difficulties.

#### **B. Resource Management Software**

The management of cluster computers includes many responsibilities from initial assembly and software installation to possible dynamic load balancing of user application modules. Originally, users of moderate-scale low-cost Beowulf-class performed most of these chores manually, ignoring some as unnecessary for dedicated use. But modern clusters supporting multiple users and a range of application and workload types on systems scaled to hundreds of gigaflops require sophisticated environments and tools to manage the plethora of system resources. Programming tools, while still in transition, have achieved a level of community-wide standardization. Such is not the case for resource management tools. These are still in a state of experimentation although there is general consensus on the basic requirements. The principal capabilities needed for commercial grade resource management include the following:

- Assembly, installation, and configuration. Setting up a cluster, whether assembled on site by staff or vendor provided, can benefit from a set of low-level tools that organize the task of installing the large suite of software and configuring the large number of system parameters. Maintaining consistency across all of the nodes can be facilitated by routines that search and validate all copies and their version numbers.

- Scheduling and allocation. Loading a parallel application program on to a cluster shared by other users and jobs requires software tools that determine which resources will be employed to perform what jobs and when. Far more complicated than on a conventional uniprocessor, cluster scheduling involves space sharing where a sys-

tem is physically partitioned into multiple subsystems to run as many jobs.

- System administration. The management of user accounts, job queues, security, backups, mass storage, log journaling, operator interface, user shells, and other house-keeping activities are essential elements of a commercial-grade computing system but impose added burden due to the multiplicity of computing resources and the diverse ways in which they may be used. PBS is an example of one software system that brings much of this capability to cluster computing.

- Monitoring and diagnosis. The complex state of a cluster, its operational status, tasks being performed, and its performance are all constantly changing. Operator tools are required to continuously monitor the behavior of the many components comprising a cluster system and quickly diagnosing hardware or software failures when they occur. A number of such tool sets have been developed by many cluster installations although no single suite has been adopted by the community as a whole.

- Parallel mass storage. Almost all computations require access to secondary storage including both local and remote disk drives for support of file systems. Commercial applications frequently use their own in-house distributed software for file management optimized around the specific needs of the application. Examples of general-purpose parallel file systems used for clusters include PPFS (http://www-pablo.cs.uiac.edu/Project/PPFS/PPFSII/PPFSIIOverview.htm), PVFS (http://parlweb.parl.Clemson.edu/pvfs), and GPFS (http://gfs.lcse.umn.edu).

- Reliability. Checkpoint and restart support software allows large programs with long run times to survive transient or hard failures of system components. Individual organizations and some vendors have developed some support for this capability although a general solution is not widely available. More difficult is the detection of errors. Software fault tolerance is a field in which strides are being made but which is still largely experimental.

While substantial advances have been made during the early 2000s, continued research and development are required to produce a common cluster environment that satisfies the requirements of a broad user community and exhibits sufficient reliability to garner confidence in the robustness and therefore utility of commodity clusters for commercial and industrial grade processing. A number of efforts are under way to synthesize a number of tools into common frameworks including the Oscar, Grendel, and RWCP projects. More than one ISV offers collections of cluster middleware including PGI and Scyld. In the long term, one or more advanced programming models and their complementing runtime execution models will have

to be developed before commodity clusters become significantly easier to program and perhaps more efficient as well for a broader range of application algorithms. The development of PSE for a range of widely used application classes may provide partial solution to the challenge of programming, at least for those special cases. PSE software presents a template to the user who then fills in the parameters with data relevant to the specific problem to be performed. This eliminates the need for detailed program development and reduces the time to solution as well as providing improved efficiency of operation. But for general-purpose cluster computing, significant improvements in ease of use may depend on next-generation parallel programming formalisms.

#### VI. SUMMARY AND CONCLUSIONS

Commodity cluster computing is growing rapidly both for high-end technical and scientific application domains and for business and commerce. The low cost, high flexibility, and rapid technology tracking are making this class of computing the platform of choice for many user domains requiring scalability and excellent price/performance. The extraordinary rate of growth in capability for commodity clusters in general and Beowulf-class systems in particular is anticipated to continue for at least the next 5 years. By 2005 to 2006, price/performance may reach \$0.10 per megaflops with systems as large as 50 teraflops operational at a few sites. There is a strong likelihood that Linux and Microsoft Windows will be the mainstream operating systems, with one or the other offered by virtually every system vendor. Both are also likely to incorporate advancements that directly enhance cluster scalability and efficiency by eliminating bottlenecks and reducing overhead. Network bandwidths of 10 Gbps will have become commonplace with network latency approaching 1  $\mu$ sec through the implementation of Infiniband. MPI-2 will be the ubiquitous programming model for parallel applications and .NET or an equivalent tool set will be employed for loosely coupled workloads, primarily in the commercial sector. Packaging will become cheaper and more compact to reduce footpad and overall system cost. Finally, systems administration tools will have reached the sophistication of mainstream servers. In 10 years, the first petaflops-scale commodity clusters will have been installed.

#### SEE ALSO THE FOLLOWING ARTICLES

COMPUTER ARCHITECTURE • COMPUTER NETWORKS • DATABASES • DATA STRUCTURES • PARALLEL COMPUTING • PROJECT MANAGEMENT SOFTWARE

#### **BIBLIOGRAPHY**

Buyya, R. (1999). "High Performance Cluster Computing," Vol. 1, Prentice Hall, Upper Saddle River, NJ.

Gropp, W., Lusk, E., and Skjellum, A. (1999). "Using MPI: Portable Parallel Programming with the Message-Passing Interface," The MIT Press, Cambridge, MA.

Pfister, G. F. (1998). "In Search of Clusters," 2nd ed., Prentice Hall, Upper Saddle River, NJ.

Seifert, R. (1998). "Gigabit Ethernet: Technology and Applications for High-Speed LANs," Addison Wesley Longman, Reading, MA.

Sterling, T. L., Salmon, J., Becker, D. J., and Savarese, D. F. (1999). "How to Build a Beowulf: a Guide to the Implementation and Application of PC Clusters," The MIT Press, Cambridge, MA.

# Keith D. Cooper Ken Kennedy Linda Torczon

Rice University

- Structure of a Compiler

- II. Recognizing Valid Programs

- III. Internal Representations

- IV. Optimization

- V. Code Generation

- VI. Summary

#### **GLOSSARY**

**Back end** The final phase of compilation, where the program is translated from the compiler's intermediate representation into operations for the target machine.

**Compiler** A program that translates an executable program from one form to another.

**Constant propagation** An optimization that discovers, at compile time, expressions that must have known constant values, evaluates them, and replaces their run-time evaluation with the appropriate value.

**Data-flow analysis** A collection of techniques for reasoning, at compile time, about the flow of values at run-time.

**Front end** The initial stage of compilation, where the program is translated from the original programming language into the compiler's intermediate representation.

**High-level transformations** Transformations performed

on an intermediate representation that is close to the source language in its level of abstraction.

**Instruction selection** The process of mapping the compiler's intermediate representation of the program into the target language produced by the compiler.

Lexical analysis That part of the compiler's front end that has the task of converting the input program from a stream of individual characters into a stream of words, or tokens, that are recognizable components of the source language. Lexical analysis recognizes words and assigns them to syntactic categories, much like parts of speech. The pass that implements lexical analysis is called a *scanner*.

List scheduling An algorithm for reordering the operations in a program to improve their execution speed. A list scheduler constructs a new version of the program by filling in its schedule, one cycle at a time. The scheduler must respect the flow of values in the original program and the operation latencies of the target machine.

Memory hierarchy management A collection of transformations that rewrite the program to change the order in which it accesses memory locations. On machines with cache memories, reordering the references can increase the extent to which values already in the cache are reused, and thus decrease the aggregate amount of tie spent waiting on values to be fetched from memory.

**Optimizer** The middle part of a compiler, it rewrites the program in an attempt to improve its *runtime* behavior. Optimizers usually consist of several distinct passes of analysis and transformation. The usual goal of an optimizer is to decrease the program's execution time; some optimizers try to create smaller programs as well.

Parallelization The task of determining which parts of the program are actually independent, and can therefore execute concurrently. Compilers that use these techniques usually treat them as high-level transformations, performing both analysis and transformations on a near-source representation of the program.

**Programming languages** Artificial (or formal) languages designed to let people specify algorithms and describe data structures, usually in a notation that is independent of the underlying target machine.

**Regular expressions** A mathematical notation for describing strings of characters. Efficient techniques can convert a collection of regular expressions into a scanner.

**Semantic elaboration** That part of a compiler's front end that checks semantic rules and produces an intermediate representation for the program. Often, semantic elaboration is coupled directly to the parser, where individual actions can be triggered as specific grammatical constructs are recognized.

**Source-to-source translator** A compiler that produces, as its target language, a programming language (rather than the native language of some target computer).

**Syntax analysis** That part of the compiler's front end that has the task of determining whether or not the input is actually a program in the source language. The parser consumes a stream of categorized words produced by the scanner and validates it against an internal model of the source language's grammatical structure (or syntax). The pass that implements syntax analysis is called a *parser*.

**Vectorization** A specialized form of parallelization that tries to expose computations suitable for SIMD, or vector, execution.

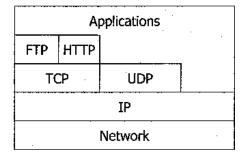

**COMPUTER PROGRAMS** are usually written in languages designed for specifying algorithms and data structures. We call such languages *programming languages*. On the other hand, the computer hardware executes op-

erations, or *instructions*, that are much less abstract than the operations in the programming language, with set of available instructions varying from computer to computer. Before a program can execute, it must be translated from the programming language in which it is written into the machine language instructions for the computer on which it will run. The program that performs this translation is called a *compiler*.

Formally, a compiler is simply a program that takes as its input an executable program and produces as its output an equivalent program. For the purpose of discussing translation, we refer to the language of the input as the *source language* and the language of the output as the *target language*. The input program is typically written in some well-known programming language, such as Fortran, C, C++, Ada, Java, Scheme, or ML. The output program is rewritten into the set of native operations of a particular computer. (Some compilers use high-level languages as their target language. Such compilers are often called *source-to-source translators*.)

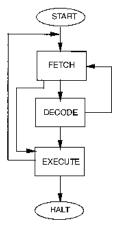

#### I. STRUCTURE OF A COMPILER

While compilers can be built as monolithic programs, more often, they are implemented as a series of distinct phases, generally organized into three major sections: a front end, an optional optimizer (or middle end), and a back end.

The front end analyzes the source program to determine whether or not it is well formed—that is, if it is a valid program in the source language. To accomplish this, it must first analyze each word in the program, classifying it into a syntactic category—a task called lexical analysis. It must then determine if the string of classified words fits into the grammatical structure of the language, a task called syntax analysis. In addition, it must check a variety of extrasyntactic rules to ensure that the source program has meaning, a process called context-sensitive analysis. Finally, it must construct an internal representation (IR) of the program for use by the later phases.

The *optimizer* takes the program, expressed in the compiler's IR, and produces an "improved" version of the program, usually expressed in the same IR. A program can be improved in different ways: it might be made to run faster; it might be made more compact in memory or secondary storage; or it might be transformed to consume less

power. To produce the improved program, the optimizer must reason about how the program will behave when it executes. It can use this knowledge to simplify, specialize, and rearrange the elements of the internal form of the program. At each step in the process, it must preserve the meaning of the program, as expressed in its externally visible behavior.

The back end maps the program, expressed in the compiler's IR, into the target language. If the target is an instruction set for a particular computer, then the back end must account for that machine's finite resources and idiosyncratic behavior. This adds significant complexity to the task of code generation. The back end must select a set of operations to implement each construct in the program. It must decide where in the computer's memory each value will reside—a task complicated by the hierarchical memory systems of modern computers, and by the fact that the fastest locations, called registers, are extremely limited in number.1 It must choose an execution order for the operations—one that preserves the proper flow of values between operations and avoids requiring the processor to wait for results. This may necessitate insertion of null operations to ensure that no operation begins to execute before its operands are ready. Many of the most challenging problems in compiler construction occur in the back end.

#### II. RECOGNIZING VALID PROGRAMS

Before the compiler can translate a source language program into a target machine program, it must determine whether or not the program is well formed—that is, whether the program is both grammatically correct and meaningful, according to the rules of the source language. This task—determining whether or not the program is valid—is the largest of the front end's tasks. If the front end accepts the program, it constructs a version of the program expressed in the compiler's internal representation. If the front end rejects the program, it should report the reasons back to the user. Providing useful diagnostic messages for erroneous programs is an essential part of the front end's work.

To address these issues, the typical front end is partitioned into three separate activities: lexical analysis, syntactic analysis, and context-sensitive analysis.

#### A. Lexical Analysis

A major difference between a programming language and a natural language lies in the mechanism that maps words into parts of speech. In most programming languages, each word has a unique part of speech, which the compiler can determine by examining its spelling. In a natural language, a single word can be mapped to several different parts of speech, depending on the context surrounding it. For example, the English words "fly" and "gloss" can be used as either noun or verb. The simpler rules used by programming languages permit the compiler to recognize and classify words without considering the grammatical context in which they appear.

To specify the spelling of words and their mapping into parts of speech, compiler writers use a formal notation called *regular expressions*. Regular expressions describe strings of symbols drawn from a finite alphabet, as well as ways to combine such strings into longer strings. First, any finite string of characters drawn from the alphabet is a regular expression. From these we can build longer strings by applying any of three rules. If *r* and *s* are regular expressions, then

- 1.  $(r \mid s)$  is a regular expression, denoting a string that is either r or s

- 2. rs is a regular expression, denoting an occurrence of r followed immediately by an occurrence of s

- 3. *r*\* is a regular expression, denoting zero or more consecutive occurrences of *r*

Using regular expressions, we can compactly specify the spelling of fairly complex words. For example, since any specific word is a regular expression, we can specify the reserved words of a programming language, e.g., **define**, **do**, **if**, and **car**, simply by listing them. We can define a more complex construct, the counting numbers over the alphabet of digits, as  $(1|2|3|4|5|6|7|8|9) (0|1|2|3|4|5|6|7|8|9)^*$ . (We read this as "a digit from 1 through 9 followed by zero or more digits from 0 through 9.") Notice that this regular expression forbids leading zeros.

We call the pass of the compiler that recognizes and classifies words the *scanner* or *lexical analyzer*. The scanner consumes a stream of characters and produces a stream of words; each annotated with its part of speech. In a modern compiler system, the scanner is automatically generated from a set of rules, specified by regular expressions. The scanners generated by this process incur small, constant cost per character, largely independent of the number of rules. For this reason, recognizers derived from regular expressions have found application in tools ranging from text editors to search engines to web-filtering software.

#### **B. Syntactic Analysis**

The job of the *syntax analyzer* is to read the stream of words produced by the scanner and decide whether or not that stream of words forms a *sentence* in the source language. To do this, the compiler needs a formal description of the source language, usually called a *grammar*. Informally, a grammar is just a collection of rules for deriving

<sup>&</sup>lt;sup>1</sup>(Possible cross reference to cache memory, registers, . . .)

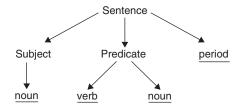

sentences in some language. For example, the following grammar describes a class of simple English sentences:

- 1. Sentence → Subject Predicate period

- 2. Subject  $\rightarrow$  noun

- 3. Subject  $\rightarrow$  adjective noun

- 4. Predicate  $\rightarrow$  verb noun

- 5. Predicate  $\rightarrow$  verb adjective

- 6. Predicate  $\rightarrow \overline{\text{verb}}$  adjective noun

In these rules, underlined, lowercase symbols are *terminal symbols* for the grammar—that is, they are actual parts of speech for words that can appear in a valid sentence. The capitalized symbols are syntactic variables called *nonterminal symbols*. Nonterminals are distinguished by the fact that they appear on the left-hand side of one or more rules. Each nonterminal is defined by a set of rules. The nonterminals thus provide structure to the grammar. Each rule describes some aspect of an English sentence and an interpretation of the nonterminal that appears on its left-hand side. We read the first rule as "a Sentence is a Subject, followed by a Predicate, followed by a period." The next two rules establish two ways to construct a Subject. The final three rules give three options for building a Predicate.

Consider the sentence "Compilers are programs." It fits the simple grammar. To see this, first convert each word to its part of speech: "noun verb noun period." To derive a sentence with this structure, we can start with Sentence and use the rules to rewrite it into the desired sentence:

| Grammatical Form           | Rule |  |

|----------------------------|------|--|

| Sentence                   | _    |  |

| → Subject Predicate period | 1    |  |

| → noun Predicate period    | 2    |  |

| → noun verb noun period    | 4    |  |

This derivation proves that any sentence with the structure "noun verb noun period" fits within the grammar's model of English. This includes "Compilers are programs" as well as "Tomatoes are horses."

We can depict this derivation graphically, as a *derivation tree*, sometimes called a *parse tree*.

The front end of a compiler does not need to derive sentences. Instead, it must solve the inverse problem—given a

stream of words, construct its derivation tree. This process is called *parsing*. The parser uses a model of the source language's grammar to automatically construct a parse tree for the input program, if such a tree exists. If this process fails, the input program, as classified by the scanner, is not a sentence in the language described by the grammar.

Tools that construct an efficient parser from a grammar are widely available. These tools, called *parser generators*, automate most of the process of building the parser, and have simple interfaces to automatically derived scanners.

#### C. Context-Sensitive Analysis

The parser, alone, cannot ensure that the source program makes sense. Consider our English sentences: "Compilers are programs" and "Tomatoes are horses." Both fit the model embodied in our grammar for simple sentences; in fact, both have the same derivation. (Remember, the derivation operates on parts of speech, not the actual words.) However, the first sentence is a cogent comment on the nature of compilers while the second sentence is nonsense. The difference between them is not grammatical—it lies in properties of the words that the grammar cannot express. The verb "are" implies a relationship of equality or similarity. Compilers are, in fact, a specific kind of program. Tomatoes and horses are dissimilar enough that it is hard to accept them as equal.

Similar correctness issues arise in computer programs. Names and values have extra grammatical properties that must be respected. A correct program must use values in ways that are consistent with their definitions. Names can have distinct meanings in different regions of the program. The definition of a programming language must specify many properties that go beyond grammar; the compiler must enforce those rules.

Dealing with these issues is the third role of the front end. To succeed, it must perform *context-sensitive* analysis—sometimes called *semantic elaboration*. This analysis serves two purposes: it checks correctness beyond the level of syntax, as already discussed, and it discovers properties of the program that play an important role in constructing a proper intermediate representation of the code. This includes discovering the lifetime of each value and where those values can be stored in memory.

Specification-based techniques have not succeeded as well in context-sensitive analysis as they have in scanning and parsing. While formal methods for these problems have been developed, their adoption has been slowed by a number of practical problems. Thus, many modern compilers use simple ad hoc methods to perform context-sensitive analysis. In fact, most parser generator systems include substantial support for performing such ad hoc tasks.

#### **III. INTERNAL REPRESENTATIONS**

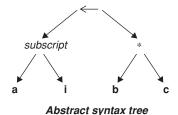

Once the compiler is broken into distinct phases, it needs an internal representation to transmit the program between them. This internal form becomes the definitive representation of the program—the compiler does not retain the original source program. Compilers use a variety of internal forms. The selection of a particular internal form is one of the critical design decisions that a compiler writer must make. Internal forms capture different properties of the program; thus, different forms are appropriate for different tasks. The two most common internal representations—the abstract syntax tree and three-address code—mimic the form of the program at different points in translation.

- The abstract syntax tree (AST) resembles the parse tree for the input program. It includes the important syntactic structure of the program while omitting any nonterminals that are not needed to understand that structure. Because of its ties to the source-language syntax, an AST retains concise representations for most of the abstractions in the source language. This makes it the IR of choice for analyses and transformations that are tied to source program structure, such as the high-level transformations discussed in Section VC.

- Three-address code resembles the assembly code of a typical microprocessor. It consists of a sequence of operations with an implicit order. Each operation has an operator, one or two input arguments, and a destination argument. A typical three-address code represents some of the relevant features of the target machine, including a realistic memory model, branches and labels for changing the flow of control, and a specified evaluation order for all the expressions. Because programs expressed in three-address code must provide an explicit implementation for all of the source language's abstractions, this kind of IR is well suited to analyses and transformations that attack the overhead of implementing those abstractions.

To see the difference between an AST and a three-address code, consider representing an assignment statement  $\mathbf{a}[\mathbf{i}] \leftarrow \mathbf{b} * \mathbf{c}$  in each. Assume that  $\mathbf{a}$  is a vector of 100 elements (numbered 0–99) and that  $\mathbf{b}$  and  $\mathbf{c}$  are scalars.

The AST for the assignment, shown on the left, captures the essence of the source-language statement. It is easy to see how a simple in-order treewalk could reprint the original assignment statement. However, it shows none of the details about how the assignment can be implemented. The three-address code for the assignment, shown on the right, loses any obvious connection to the source-language statement. It imposes an evaluation order on the statement: first **b**, then **c**, then **b** \* **c**, then **i**, then **a[i]**, and, finally, the assignment. It uses the notation@**b** to refer to **b**'s address in memory—a concept missing completely from the AST.

Many compilers use more than one IR. These compilers shift between representations so that they can use the most appropriate form in each stage of translation.

#### IV. OPTIMIZATION

A source language program can be mapped into assembly language in many different ways. For example, the expression 2 \* x can be implemented using multiplication, using addition (as x + x), or if x is an unsigned integer, using a logical shift operation. Different ways of implementing an operation can have different costs. Over an entire program, these cost differences can mount up.

Compiler optimization is the process by which the compiler rewrites the internal representation of a program into a form that yields a more efficient target-language program. The word "optimization" is a misnomer, since the compiler cannot guarantee optimality for the resulting code. In practice, optimizers apply a fixed sequence of analyses and transformations that the compiler writer believes will produce better code.

Optimizers attempt to improve the program by analyzing it and using the resulting knowledge to rewrite it. Historically, optimizers have primarily focused on making the program run faster. In some contexts, however, other properties of the program, such as the size of the compiled code, are equally important.

#### A. Static Analysis of Programs

To improve a program, the optimizer must rewrite the code (or its IR form) in a way that produces better a target language program. Before it can rewrite the code, however, the compiler must prove that the proposed transformation

| LOAD VAR  | @b                  | $\Rightarrow r_1$ |

|-----------|---------------------|-------------------|

| LOAD VAR  | @c                  | $\Rightarrow r_2$ |

| Mult      | $r_1, r_2$          | $\Rightarrow r_3$ |

| LOAD VAR  | @i                  | $\Rightarrow r_4$ |

| MULTIMMED | r <sub>4</sub> , 4  | $\Rightarrow r_5$ |

| AddImmed  | r <sub>5</sub> , @a | $\Rightarrow r_6$ |

| STORE     | r <sub>3</sub>      | $\Rightarrow r_6$ |

Three-address code

is *safe*—that is, the transformation does not change the results that the program computes—and likely to be *profitable*—that is, the resulting code will be an improvement over the existing code. To accomplish this, the compiler analyzes the program in an attempt to determine how it will behave when it runs. Because the compiler performs the analysis before the program runs, the analysis is considered a static analysis. In contrast, an analysis built into the running program would be a dynamic analysis.

Static analysis takes many forms, each one tailored to address a particular problem in the safety or profitability of optimization. One such problem is *constant propagation*—discovering variables whose run-time values can be determined at compile time. If the compiler can discover that  $\mathbf{x}$  always has the value 2 at a particular point in the program, it can specialize the code that uses  $\mathbf{x}$  to reflect that knowledge. In particular, if  $\mathbf{x}$  has the value 2 in an expression  $\mathbf{x} * \mathbf{y}$ , it can replace the expression with  $\mathbf{2} * \mathbf{y}$  or with  $\mathbf{y} + \mathbf{y}$ , either of which may be faster than a generic multiply. (The former avoids referring to  $\mathbf{x}$ , with a possible memory reference, while the latter also replaces the multiply operation with an addition, which may be cheaper.)

Analyses such as constant propagation are formulated as problems in *data-flow analysis*. Many data-flow problems have been developed for use in optimization. These include the following:

- Finding redundancies: An expression is redundant if, along any path that reaches it, that value has already been computed. If the compiler can prove that an expression is redundant, it can replace the expression with its previously computed value.

- Live variable analysis: A variable is live at some point in the code if there exists a path from that point to a use of its value. With the results of live variable analysis, the compiler can stop preserving a variable at the point where it stops being live.

- *Very-busy expressions*: An expression is *very busy* at some point if it will be used, along every path leaving that point before one of its inputs is redefined. Moving the expression to the point where it is very busy can eliminate unneeded copies of the expression, producing a smaller target program.

These problems are formulated as systems of equations. The structure of the equations is dictated by the control-flow relationships in the program. The solutions to the equations are found by using general solvers, analogous to Gaussian Elimination, or by using specialized algorithms that capitalize on properties of the program being analyzed.

#### **B. Classic Scalar Transformations**

To apply the results of analysis, the compiler must rewrite the code in a way that improves it. Hundreds of optimizing transformations have been proposed in the literature. These techniques address a wide range of problems that arise in the translation of programming languages. Examples include reducing the overhead introduced by source-language abstractions, managing hardware features such as memory, and general strategies that use properties such as commutativity and associativity to speed expression evaluation.

Among the transformations that you will find in a modern optimizer are as follows: